# **Industrial Automation**

(Automação de Processos Industriais)

http://users.isr.ist.utl.pt/~pjcro/courses/api1011/api1011.html

#### Faculty:

Prof. Paulo Jorge Oliveira pjcro @ isr.ist.utl.pt Tel: 21 8418053

Prof. José Gaspar jag @ isr.ist.utl.pt Tel: 21 8418293

# **Objectives:**

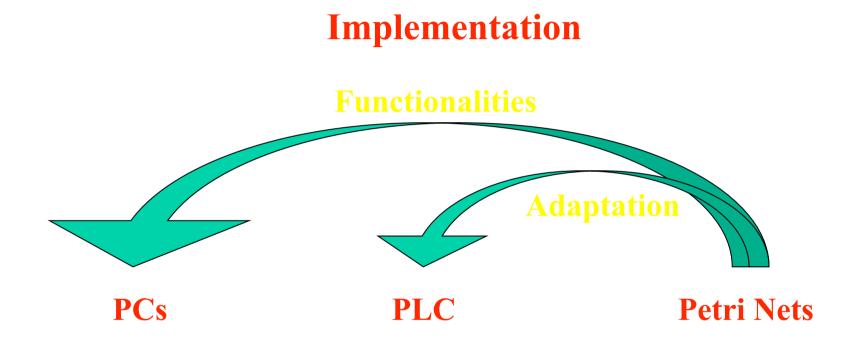

- Analysis of systems for industrial automation.

- Methodologies for the implementation of solutions in industrial automation.

- Programming languages of PLCs (Programmable Logic Controllers).

- CAD/CAM and Computerized Numerical Controlled machines.

- Discrete Event Systems Modeling.

- Supervision of Processes in Industrial Automation.

# Syllabus:

#### **Chap. 1 – Introduction to Automation [1 week]**

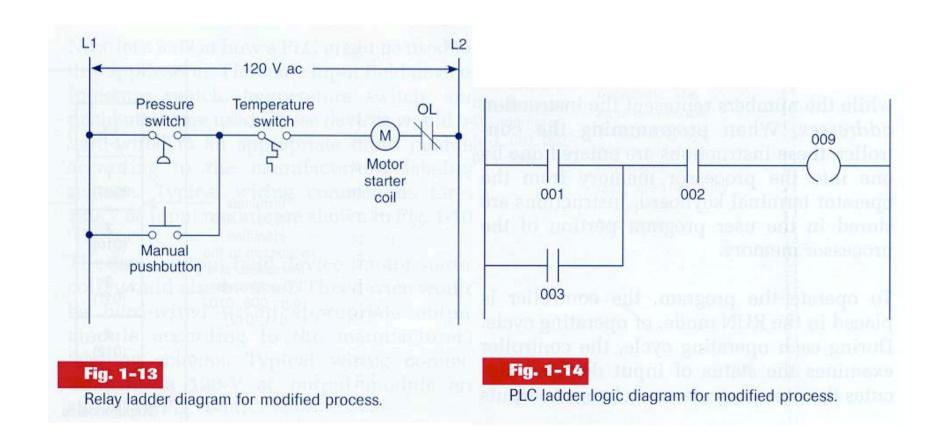

Introduction to components in industrial automation. Introduction to methodologies for problem modeling. Cabled logic versus programmed logic.

#### Chap. 2 – Introduction to PLCs [2 weeks]

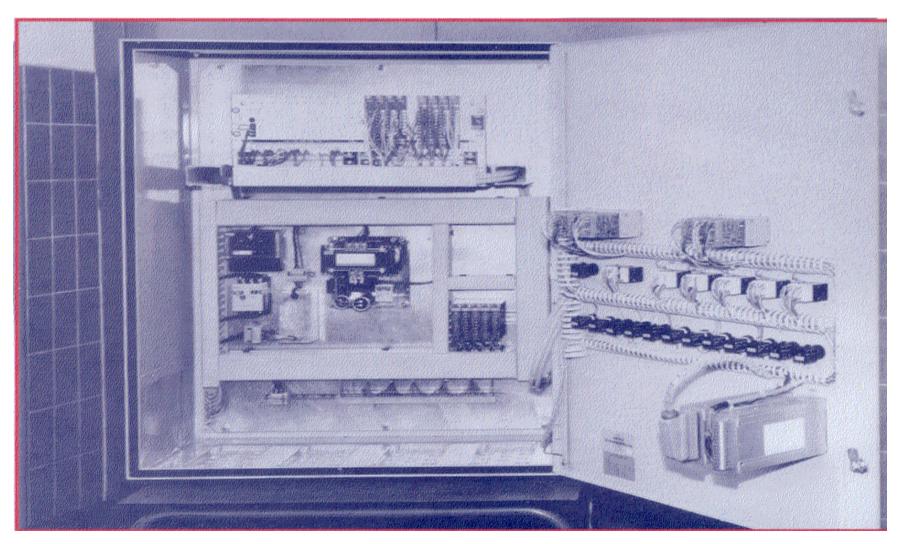

Components of Programmable Logic Controllers (PLCs). Internal architecture and functional structure. Input / output Interfaces. Interconnection of PLCs.

## Chap. 3 – PLCs Programming Languages [2 weeks]

Standard languages (IEC-1131-3):

Ladder Diagram; Instruction List and Structured Text. Software development resources.

# Syllabus (cont.):

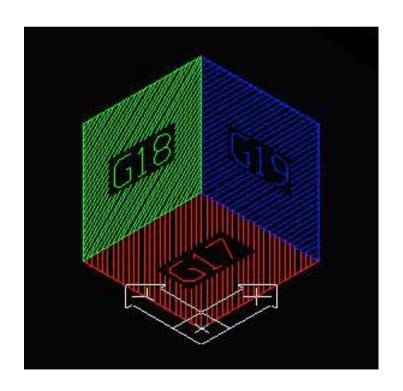

# Chap. 4 - GRAFCET (Sequential Function Chart) [1 week]

The GRAFCET norm. Elements of the language.

Modeling techniques using GRAFCET.

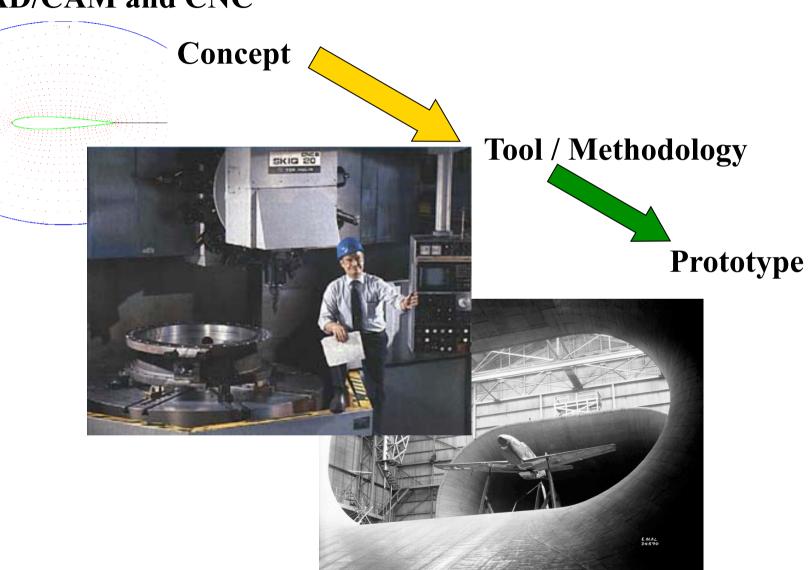

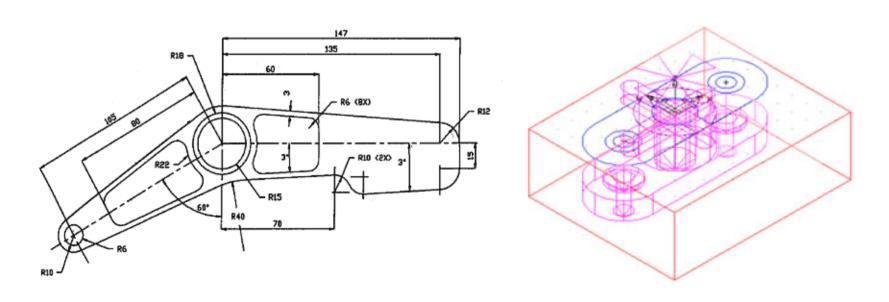

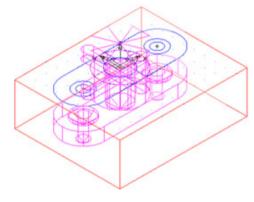

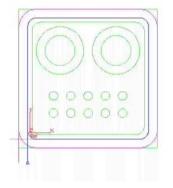

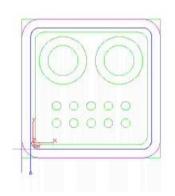

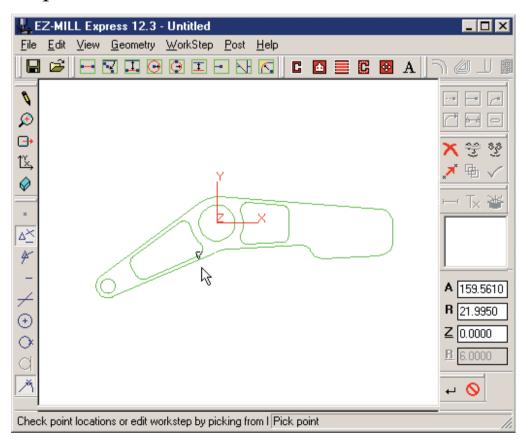

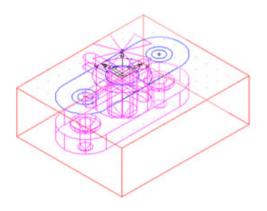

## Chap. 5 – CAD/CAM and CNC Machines [1 week]

Methodology CAD/CAM. Types of Computerized Numerical Controlled machines. Interpolation of trajectories. Flexible fabrication cells.

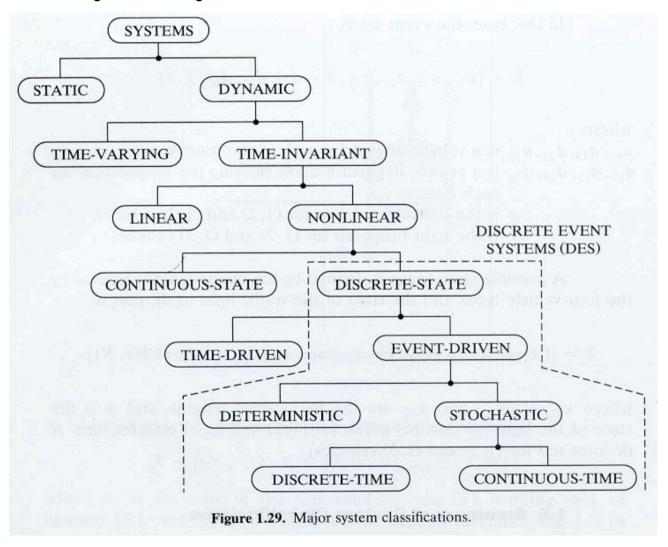

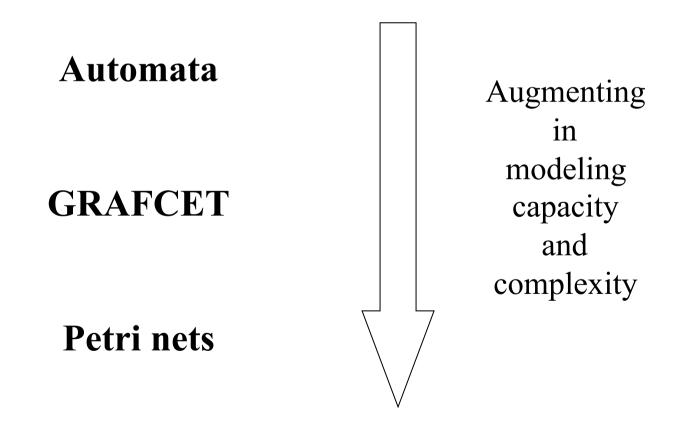

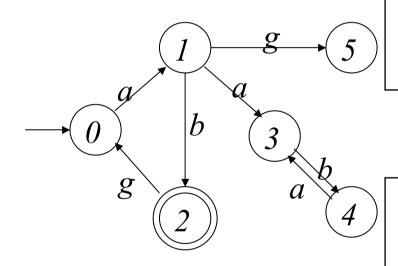

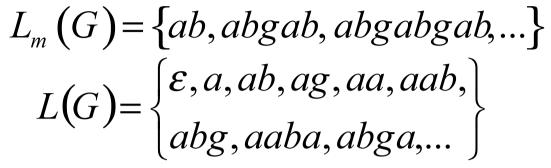

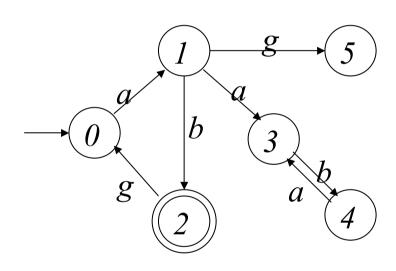

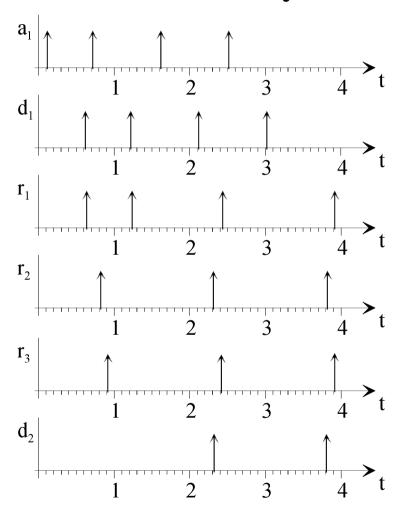

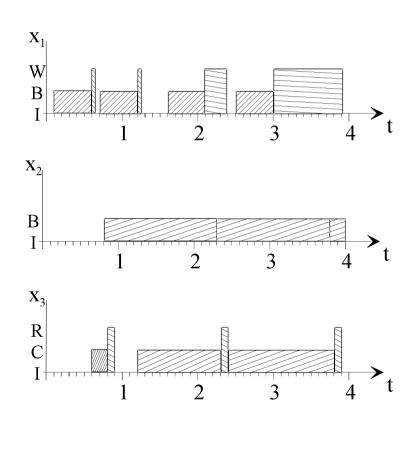

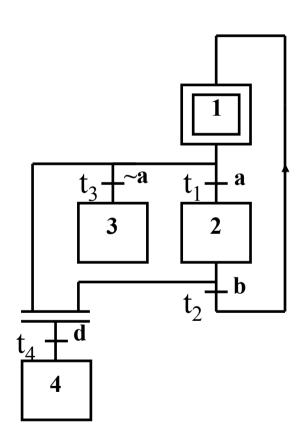

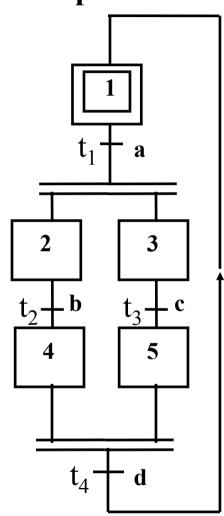

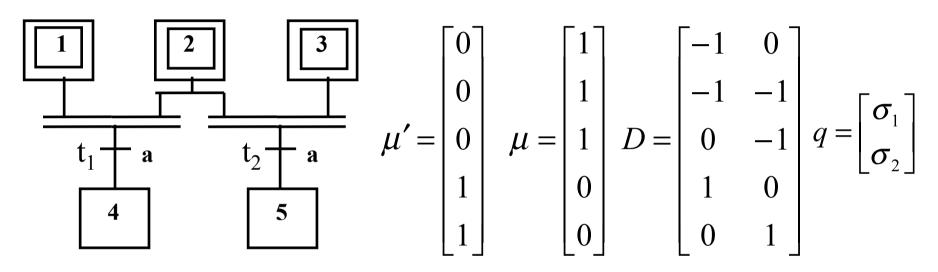

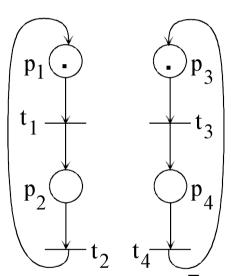

### Chap. 6 – Discrete Event Systems [1 week]

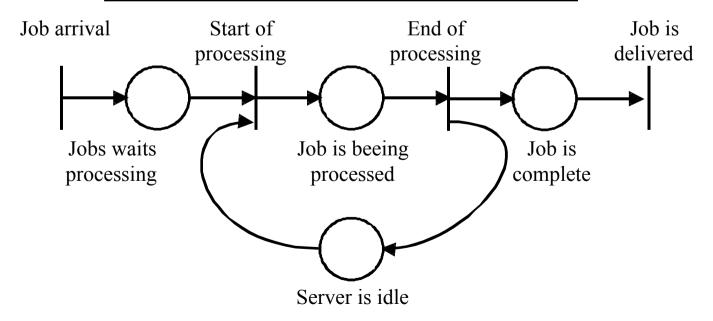

Modeling of discrete event systems (DESs).

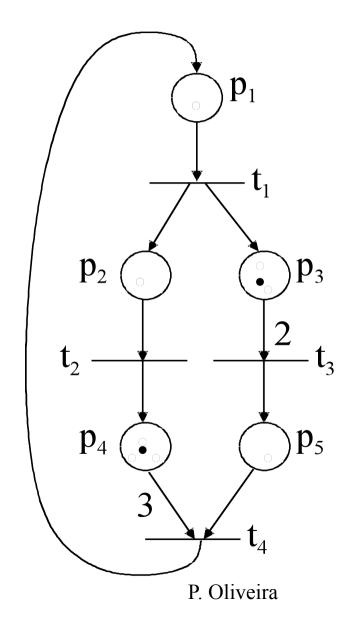

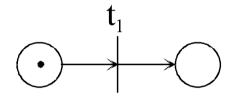

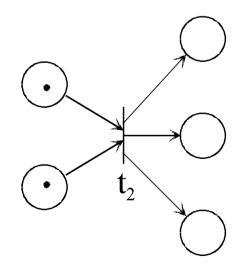

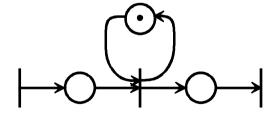

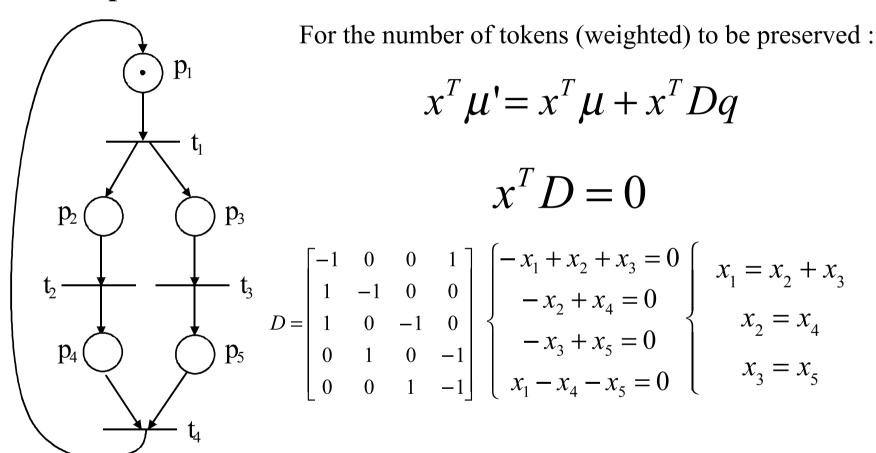

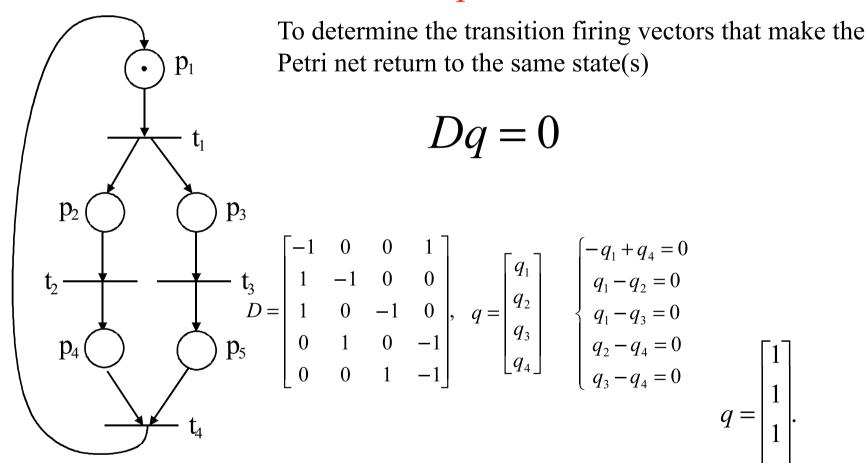

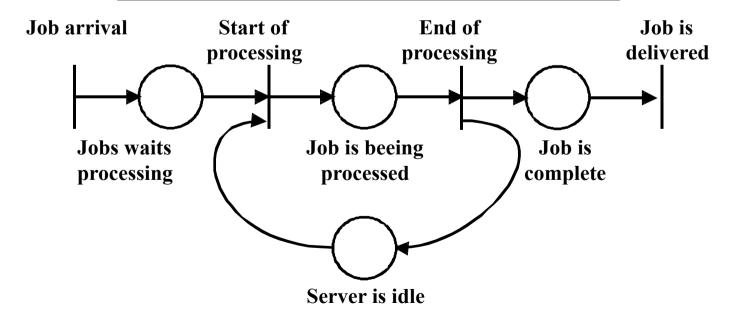

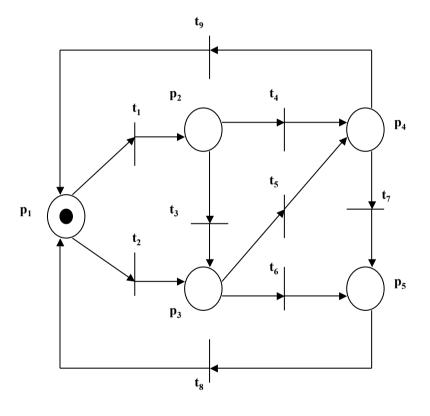

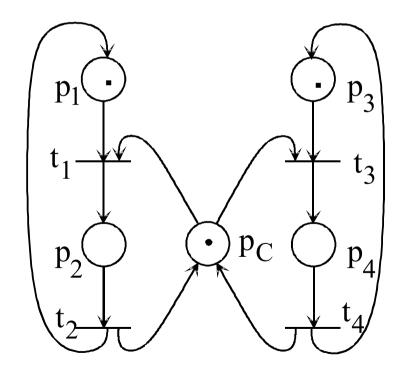

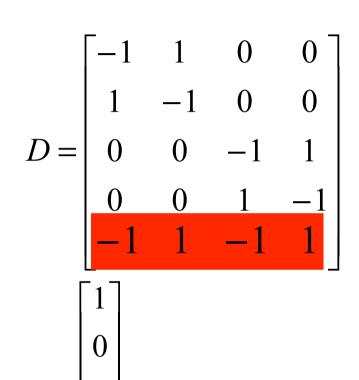

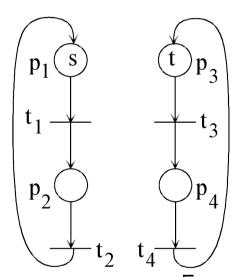

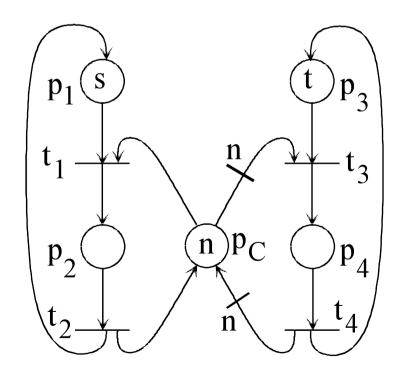

Automata. Petri networks. State and dynamics of PNs.

# Syllabus (cont.):

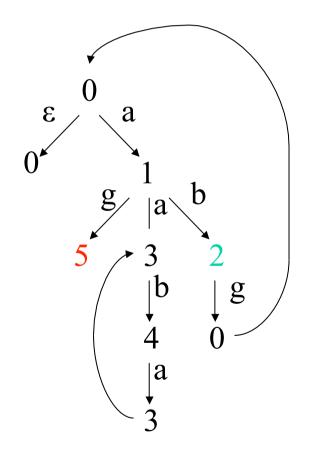

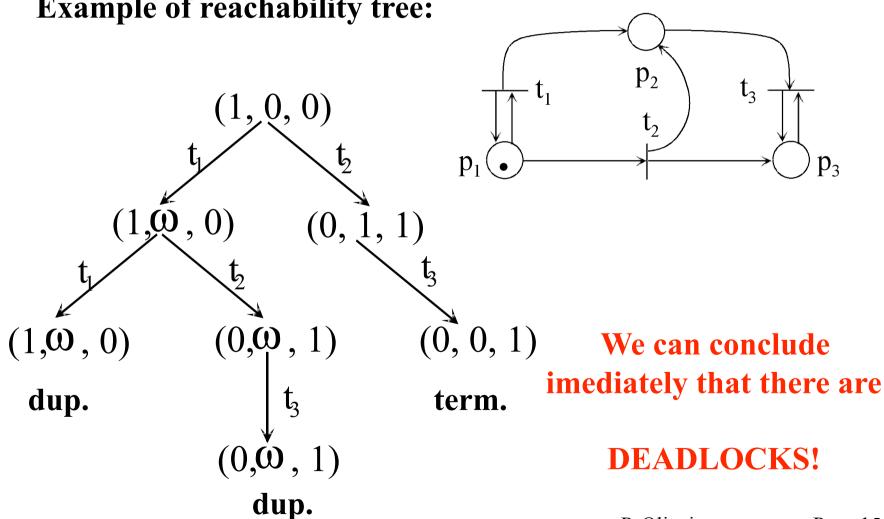

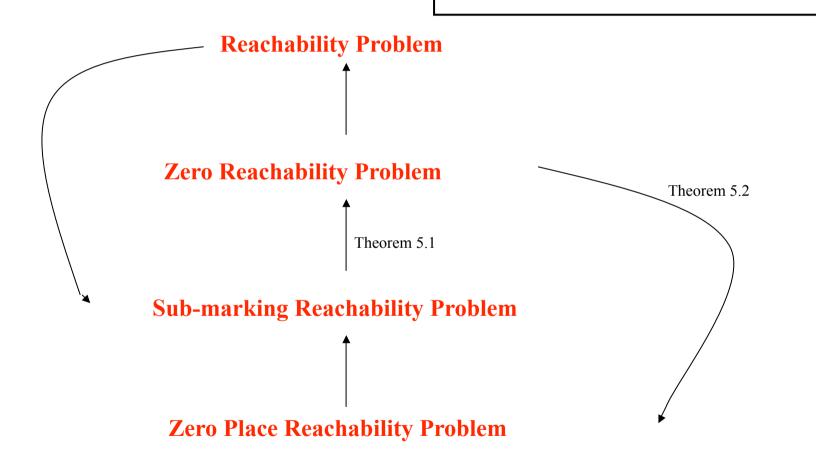

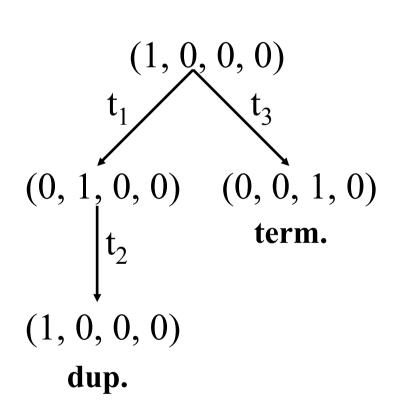

#### Chap. 7 – Analysis of DESs [2 weeks]

Properties of DESs. Methodologies for the analysis of DESs: the reachability graph and the matricial equation method.

## Chap. 8 – DESs and Industrial Automation [1 week]

Relations GRAFCET / Petri networks.

Analysis of industrial automation solutions as DESs.

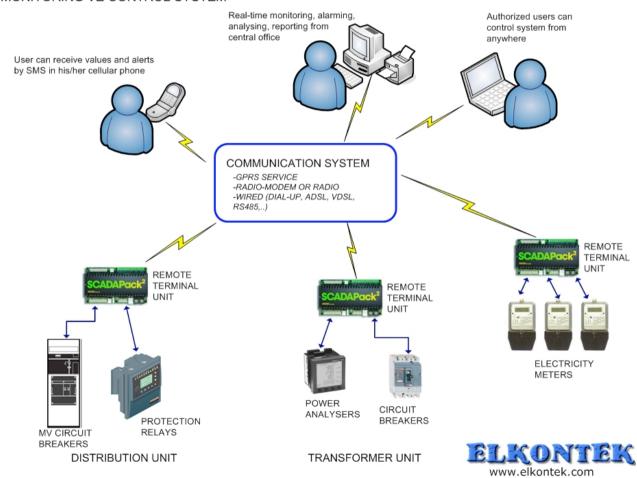

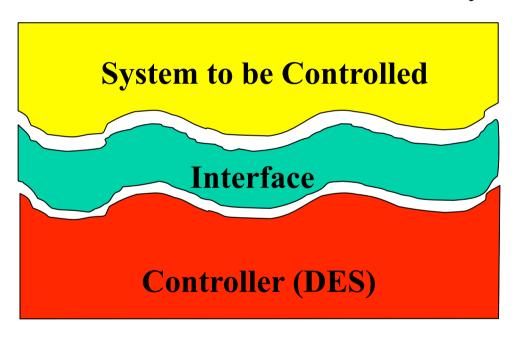

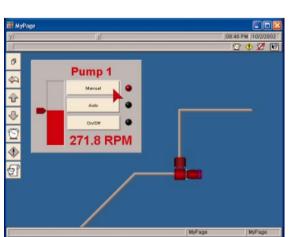

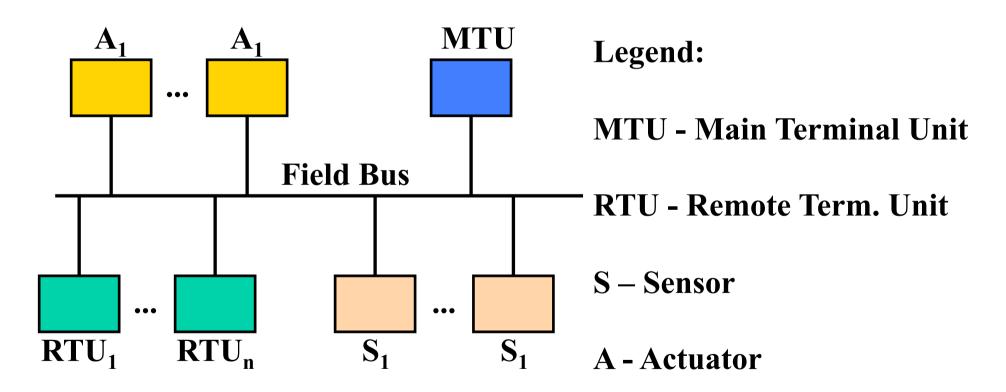

### Chap. 9 – Supervision of Industrial Processes [2 weeks]

Methodologies for supervision. SCADA.

Synthesis based on invariants. Examples of application.

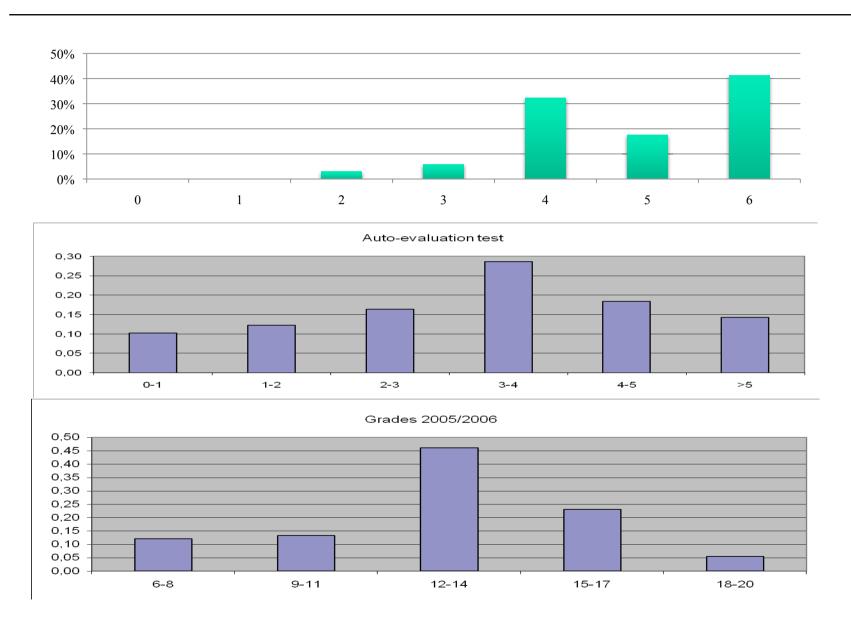

# Assessment and grading:

- 2 Preliminary laboratory assignments training purposes (0% of the final grade).

- 2 Laboratory assignments (20%+20% of the final grade). Groups of 3 students.

- 1 Seminar (20% of the final grade). Topics to be selected with each group.

- Exams (40% of the final grade). Two written.

Upon student choice, the second exam can be oral.

- Minimum grade: 9.5/20.0 val. in each component.

- Oral discussion for students with grade > 17/20 valores .

Extra 1 (one) valor for students attending more than 50% of recitations.

## **Schedule (suggested)**

October 1st 2010

## Schedule (according to IST-GOP):

• Recitation classes

| Monday | 11.00  h - 12.30 h | Ea5 |

|--------|--------------------|-----|

| Friday | 11.00  h - 12.30 h | Ea4 |

• Lab. Classes

Monday 09.30h – 11.00h L1 LSDC4 Friday 09.30h – 11.00h L2 LSDC4

Third session needed?

• Groups register for the Laboratory

# **Bibliography:**

- Automating Manufacturing Systems with PLCs, Hugh Jack (online version available).

- Peterson, James L., "Petri Net Theory and the Modeling of Systems", Prentice-Hall, 1981.

- •Modeling and Control of Discrete-event Dynamic Systems with Petri Nets and other Tools, Branislav Hruz and MengChu Zhou, 2007. New reference...

- --- secondary---

- Programmable Logic Controllers, Frank D. Petruzella, McGraw-Hill, 1996.

- Petri Nets and GRAFCET: Tools for Modeling Discrete Event Systems, R. DAVID, H. ALLA, New York: PRENTICE HALL Editions, 1992.

- Computer Control of Manufacturing Systems, Yoram Koren, McGraw Hill, 1986.

- Cassandras, Christos G., "Discrete Event Systems Modeling and Performance Analysis", Aksen Associates, 1993.

- Moody, J. e Antsaklis, Supervisory Control of Discrete Event Systems, Kluwer Academic Publishers, 1998.

P. Oliveira Page 9

# **Industrial Automation**

(Automação de Processos Industriais)

## **Introduction to Automation**

http://www.isr.ist.utl.pt/~pjcro/courses/api1011/api1011.html

Prof. Paulo Jorge Oliveira

pjero @ isr.ist.utl.pt

Tel: 21 8418053 ou 2053 (internal)

### **Cap. 1 – Introduction to Automation [1 week]**

Introduction to components in industrial automation.

Introduction to methodologies for problem modeling.

Cabled logic versus programmed logic versus networked logic.

Methodologies of work.

**API**

# Components used in industrial automation

The production of increasing amounts of goods requires the storage and handling of large quantities of resources.

The use of specialized, automatic tools are mandatory.

Consistent trend in the last three centuries (since the Industrial Revolution).

Automation was also fostered by the invention of computers,

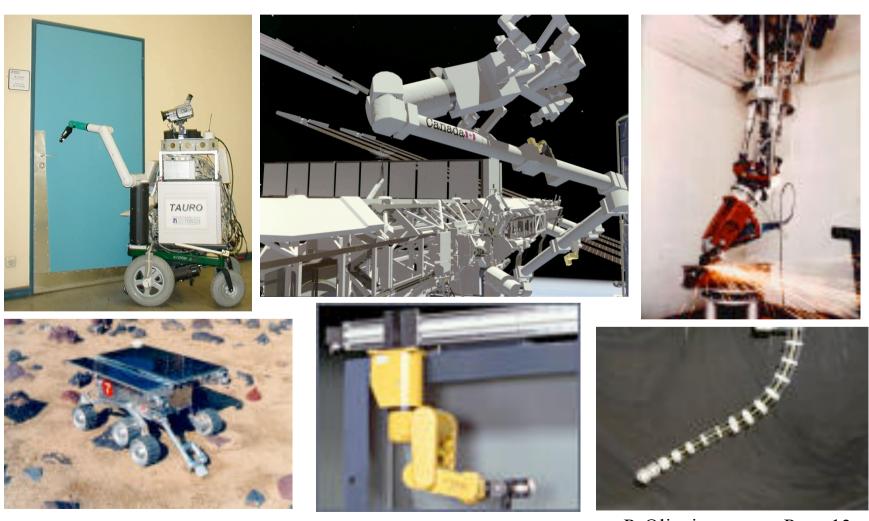

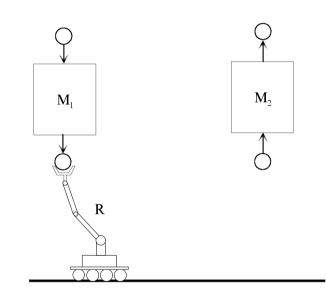

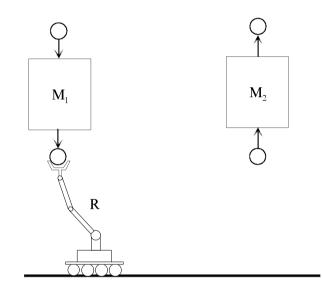

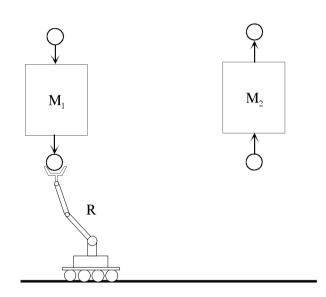

## **Robotic Manipulators**

### **End Effectors**

### **Robotic Manipulators**

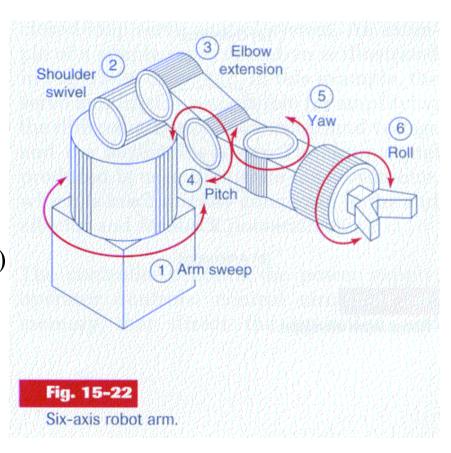

#### **Major characteristics:**

- Number of degrees of freedom

- Types of joints (prismatic/revolution/...)

- Programming tools and environments (high level languages, teach pendent, ...)

- Workspace

- Accuracy, fiability

- Payload and robustness

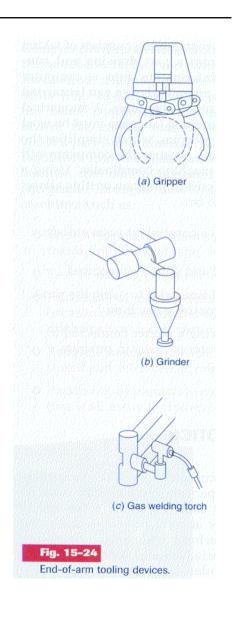

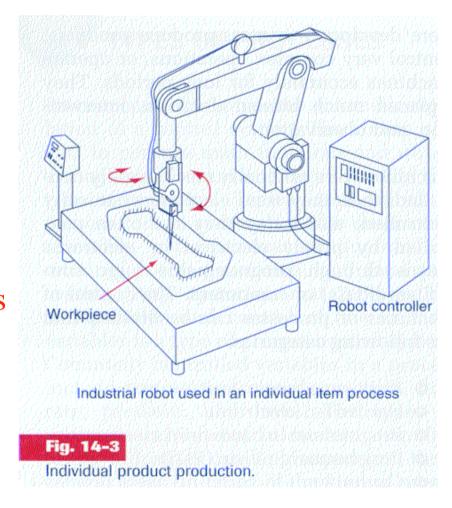

# **Robotic Manipulators** Workspace: **Examples** (b) Grinder (b) Articulated (c) Gas welding torch Fig. 15-23 (a) Cylindrical Robot work envelope. End-of-arm tooling devices.

### **Robotic Manipulators**

#### Central problems to adress and solve:

- Direct kinematics

- Inverse Kinematics

- Trajectory generation

- Coordinate frames where tasks are specified

- Level of abstraction of the programming languages

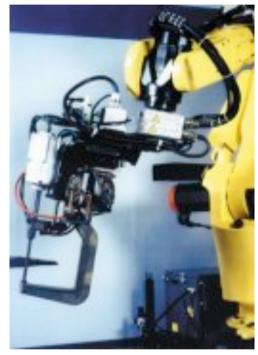

#### **Robotic Manipulators**

Use in Flexible

Cells of Fabrication:

it is required that the manipulators have correct interfaces for the synchonization and inputs for external commands.

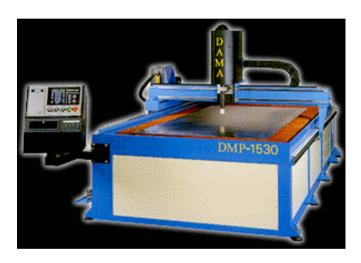

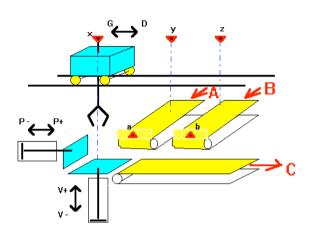

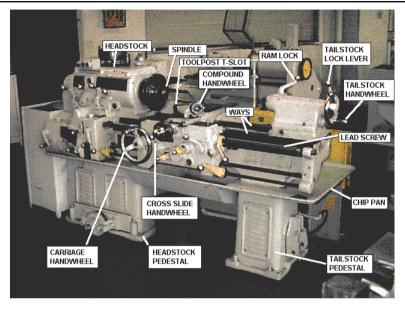

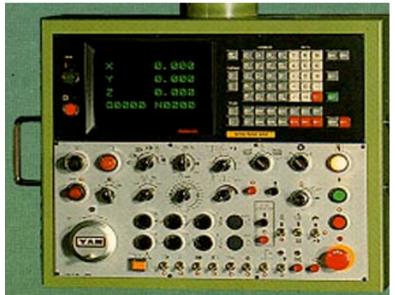

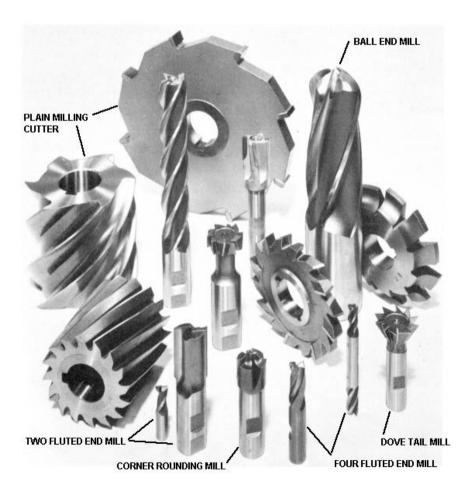

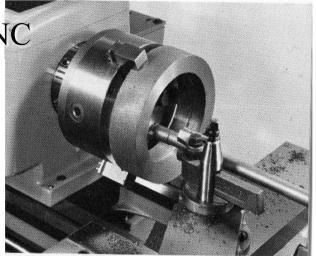

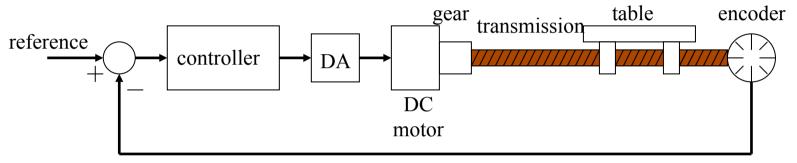

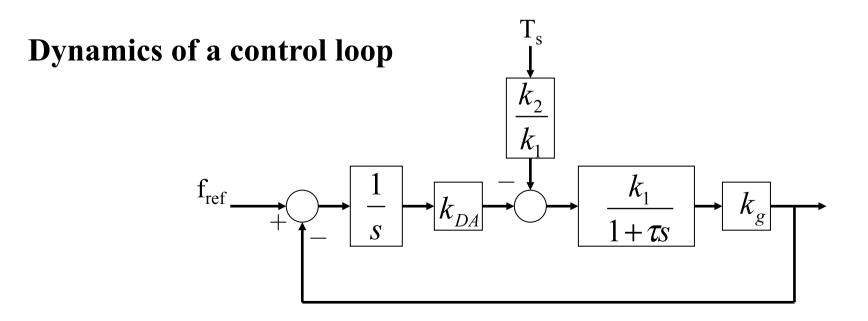

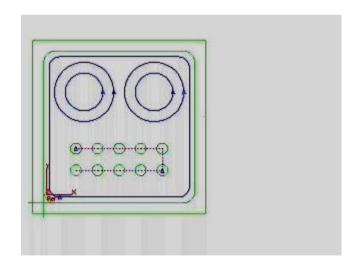

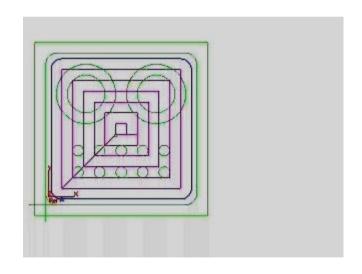

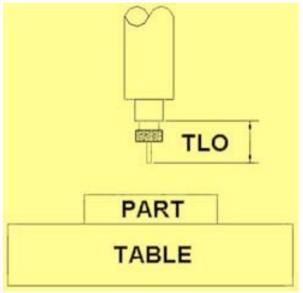

### **Computerized Numerical Controlled Machines**

#### **Major characteristics:**

- Number of degrees of freedom

- Interpolation methods

- Load/unload automation, and also in tool change

- Programming (high level languages, teach pendent, ...)

- Workspace

- Accuracy, reliability

- Payload and robustness

- Interface

- Synchronization with exterior

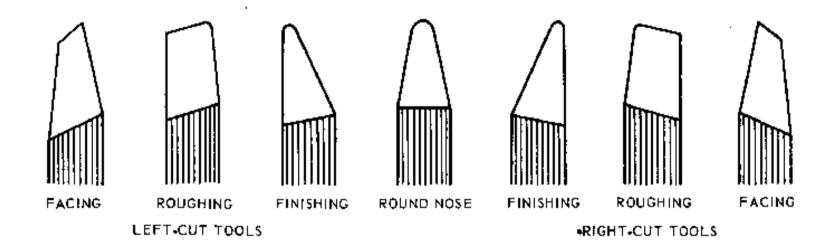

#### **Examples:**

Milling, Lathes, ...

## **Computerized Numerical Controlled Machines**

### **Solutions for Handling materials**

#### For transport...

#### **Major characteristics:**

- Load/unload automation

- Accuracy, reliability

- Payload and robustness

- Interface

- Synchronization with exterior

### **AGVs (Automatic Guided Vehicles)**

#### **Major characteristics:**

- Load/unload automation

- Accuracy, reliability

- Payload and robustness

- Interface

- Synchronization with exterior

## **AGVs (Automatic Guided Vehicles)**

#### **Example of fleet operating in industry**

#### **Actuation**

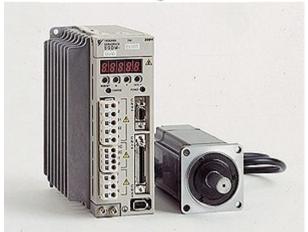

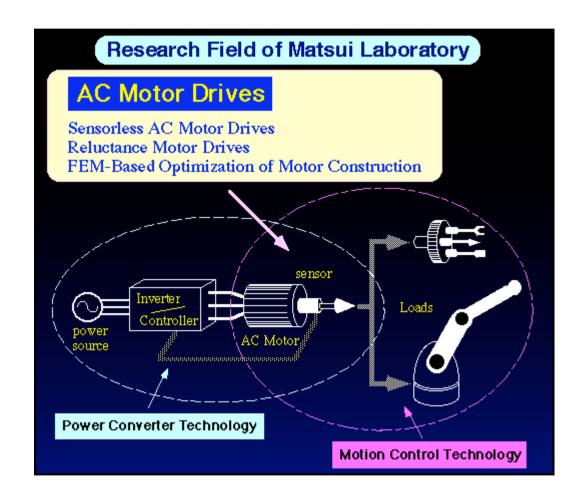

#### **Motors**

#### Major characterísticas:

- Tipe of start

- Tipe of control

- Accuracy, reliability

- Payload and robustness

- Interface with exterior

- Synchronization

## Exemple of AC motor, with driver

## **Specific Components**

## Factury example: production of aluminium packs

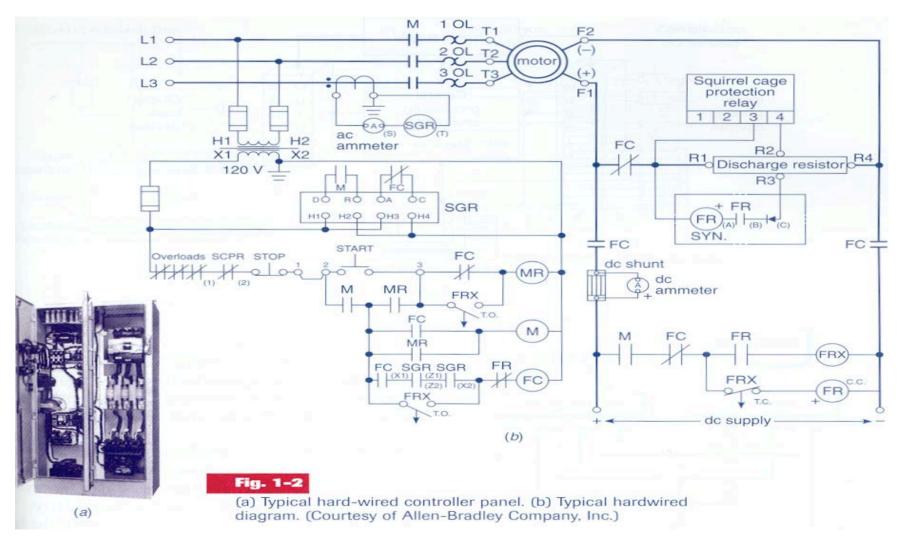

# Cabled Logic versus ...

# ... versus Programmed Logic ...

# ... versus Networked Logic

MIDDLE AND LOW VOLTAGE

ELECTRICITY DISTRIBUTION NETWORKS

MONITORING VE CONTROL SYSTEM

# Introduction to methodologies

for problem modeling

in

**Industrial Automation**

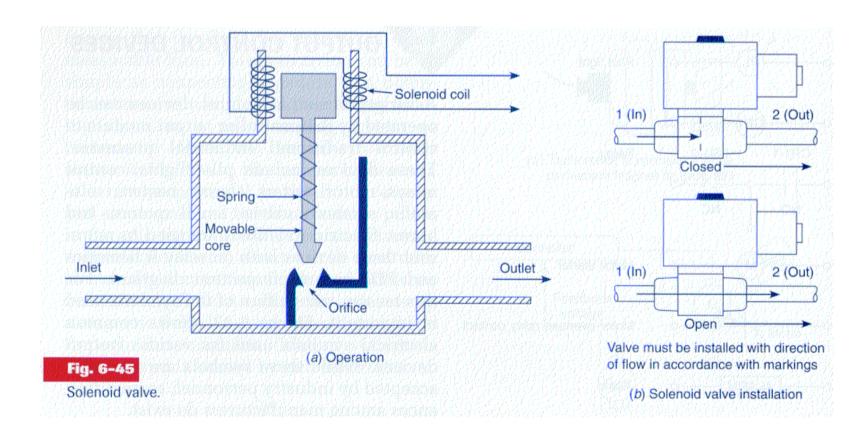

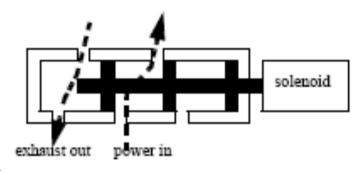

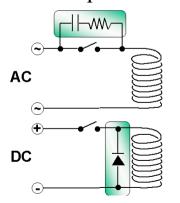

#### **Solenoide Valve**

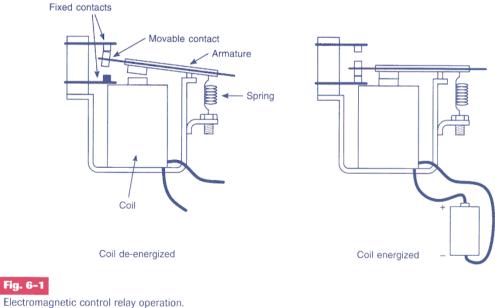

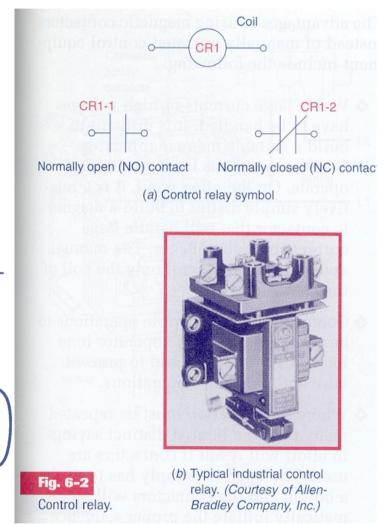

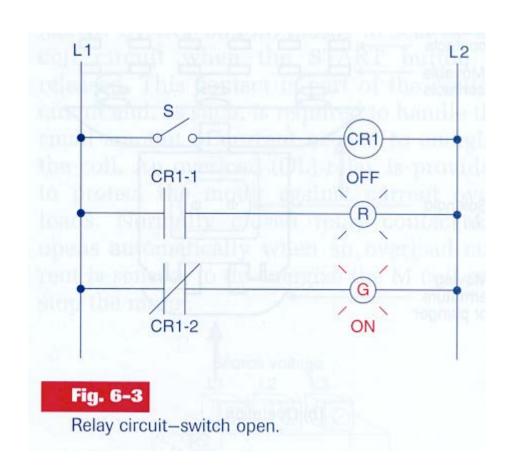

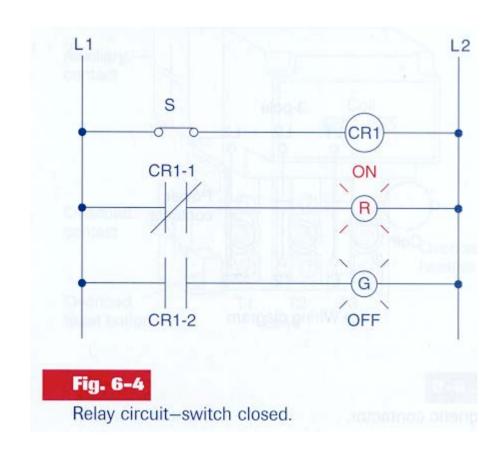

## **Command Relay**

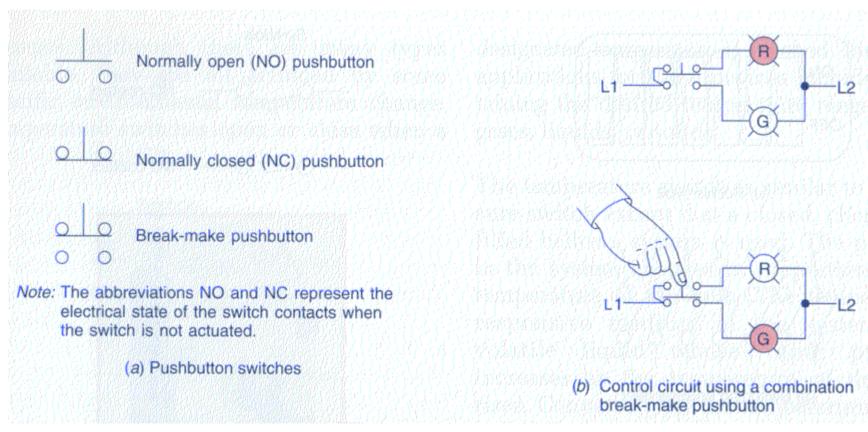

#### **Push buttons**

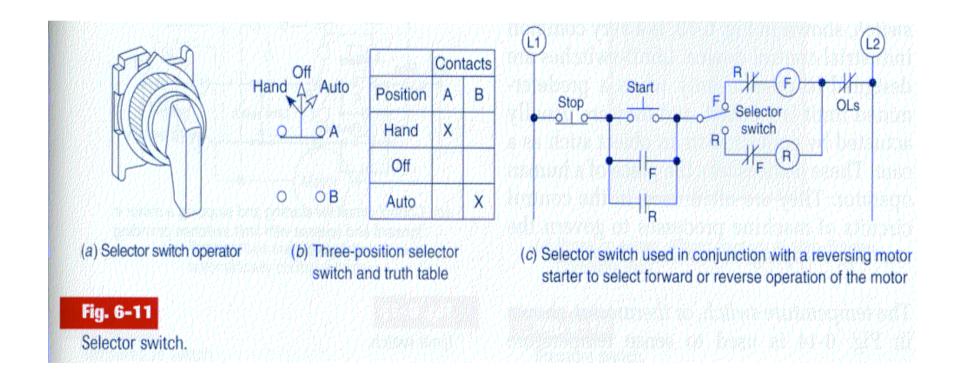

#### **Selector with three positions**

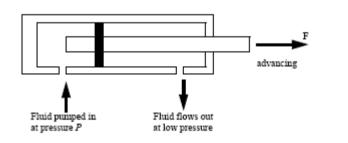

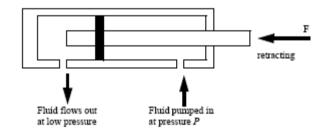

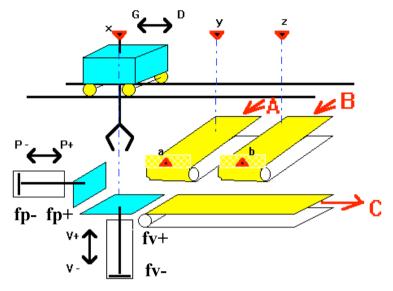

### Cylinders (Pneumatics)

For Force:

$$P = \frac{F}{A}$$

$F = PA$

where,

P = the pressure of the hydraulic fluid

A = the area of the piston

F = the force available from the piston rod

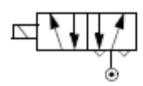

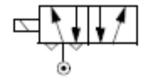

# Valves(Electro-pneumatics)

The solenoid has two positions and when actuated will change the direction that fluid flows to the device. The symbols shown here are commonly used to represent this type of valve.

# **Sensors**

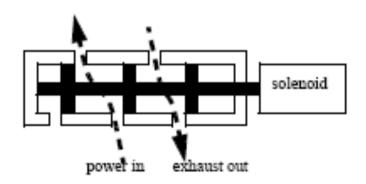

#### **Pressure Switch**

Hand

OFF

Auto

Pressure switch

(c) Starter operated by pressure switch

Fig. 6-15 (continued)

Pressure switch.

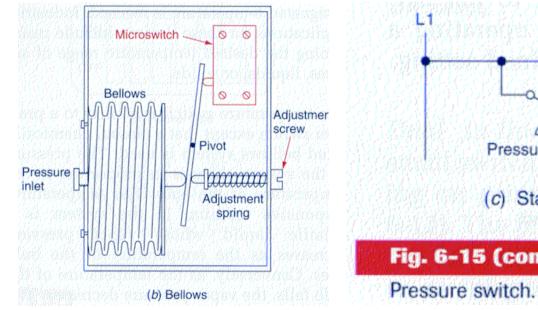

# **Temperature**

#### **Sensors**

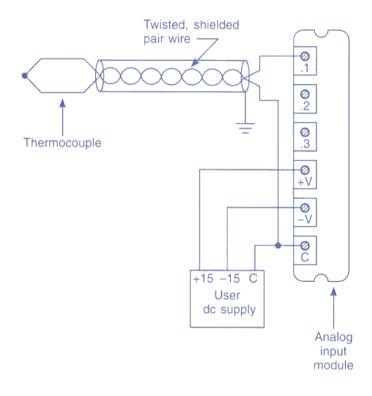

## **Termocouple**

#### Fig. 2-12

Typical thermocouple connection to an analog input module.

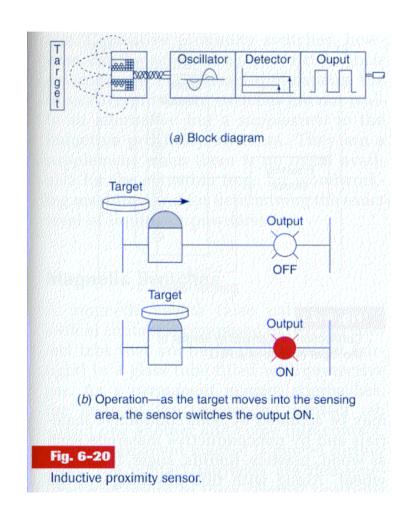

# **Proximity detector**

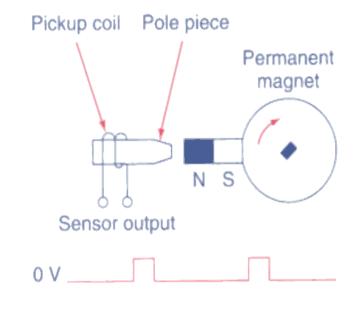

# **Magnetic detector**

Fig. 6-42

Magnetic pickup sensor.

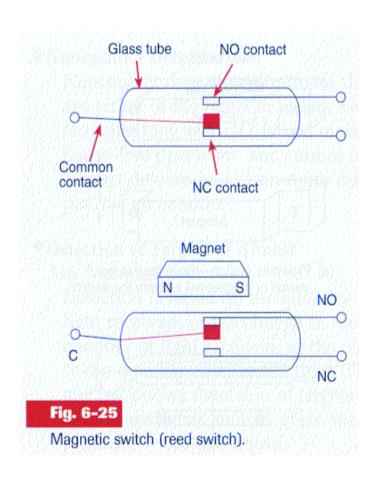

# Magnetic switch

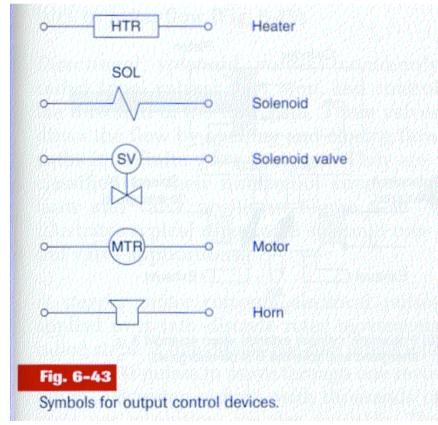

# Symbols associated to all components

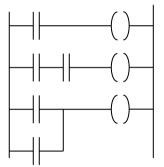

#### **Standards**

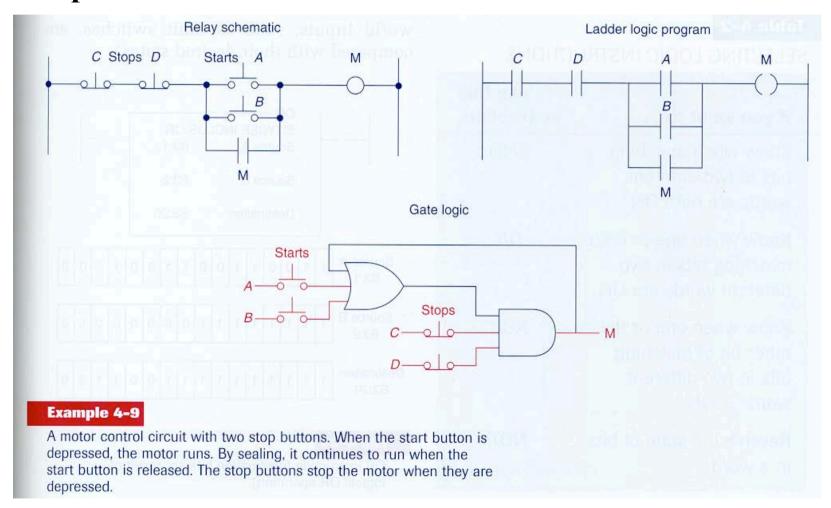

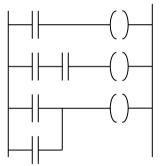

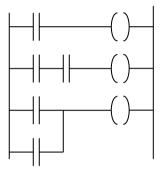

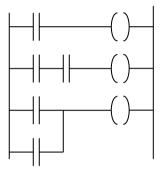

Ladder Diagram

Or

Contact Diagram

# Methodologies for the implementation of solutions in industrial automation

# Contacts diagram

Example

# **Example:**

$$X = \overline{A}$$

$$A \qquad X$$

$$0 \qquad 1$$

$$1 \qquad 0$$

EOR.

NOT

# **Logic Functions**

NAND

NOR.

$$X = A \oplus B$$

A B X

0 0 0

0 1 1

1 0 1

1 1 0

# **Example:**

# To exploit the advantages of Programmed Logic

# **Industrial Automation**

(Automação de Processos Industriais)

# **Introduction to PLCs**

http://www.isr.ist.utl.pt/~pjcro/courses/api0910/api0910.html

Prof. Paulo Jorge Oliveira pjcro @ isr.ist.utl.pt Tel: 21 8418053 ou 2053 (internal)

# Syllabus:

**Chap. 1 – Introduction to Automation [1 week]**

• • •

## Chap. 2 – Introduction to PLCs [2 weeks]

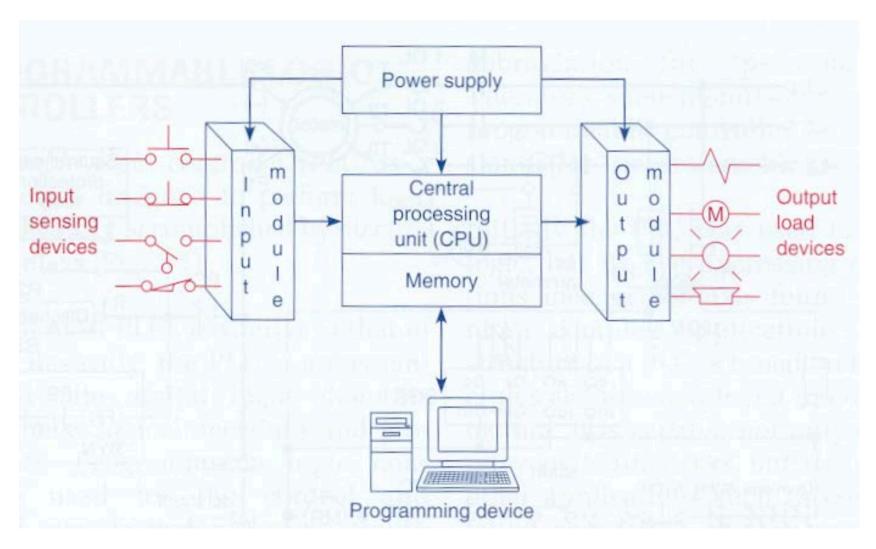

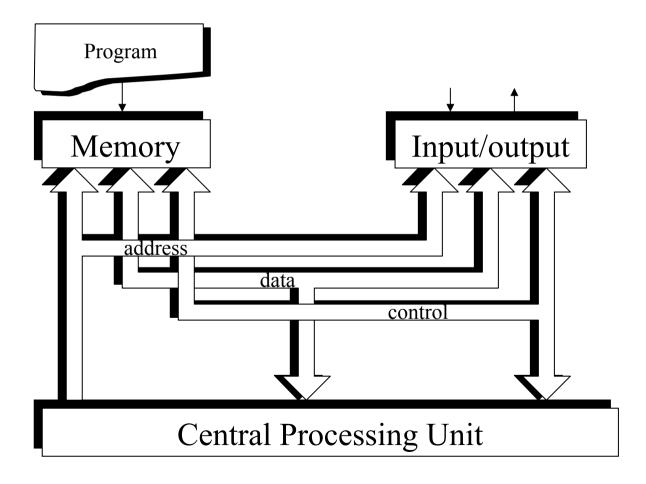

Components of Programmable Logic Controllers (PLCs). Internal architecture and functional structure. Input / output interfaces. Interconnection of PLCs.

...

### Chap. 3 – PLCs Programming Languages [2 weeks]

#### Some resorces available online on PLCs

History: <a href="http://www.plcs.net/chapters/history2.htm">http://www.plcs.net/chapters/history2.htm</a>

Tutorial: <a href="http://www.koldwater.com/downloadform.htm">http://www.koldwater.com/downloadform.htm</a>

http://www.htservices.com/Tutorials/plctutorial1.htm

http://www.sea.siemens.com/step/templates/lesson.mason?plcs:1:1:1

Simulators: <a href="http://www.thelearningpit.com/psim/psim.html">http://www.thelearningpit.com/psim/psim.html</a>

<u> http://www.keyence.com/plc/kvl.htm</u>

http://www.autoware.com/english/demo.htm

http://tytang.hypermart.net/cgi-bin/frame.pl?file=PLC sim/index.html

http://www.thelearningpit.com/psim/psim.html

Bibliography: Automatic Manufacturing Systems with PLCs, Hugh Jack

(online version available)

Programming Logic Controller s, Frank D. Petruzella

•••

Standards: <a href="http://www.plcopen.org/">http://www.plcopen.org/</a>

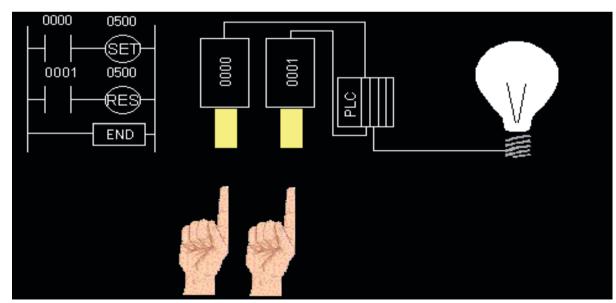

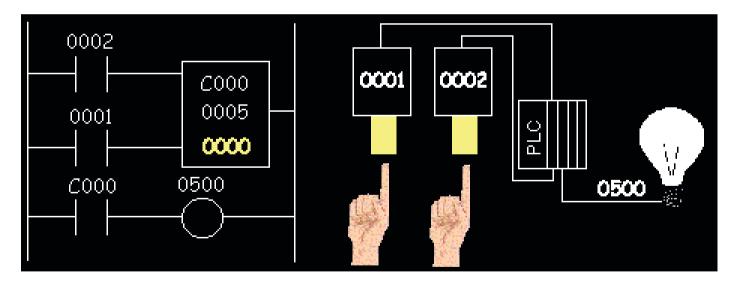

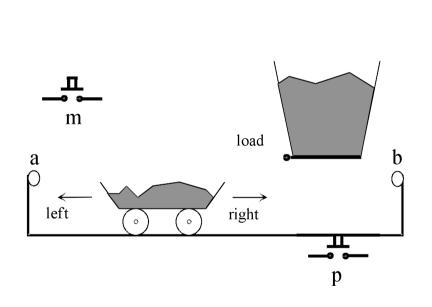

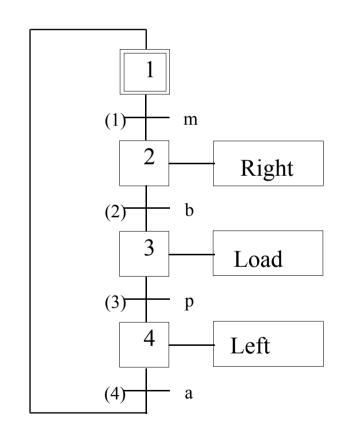

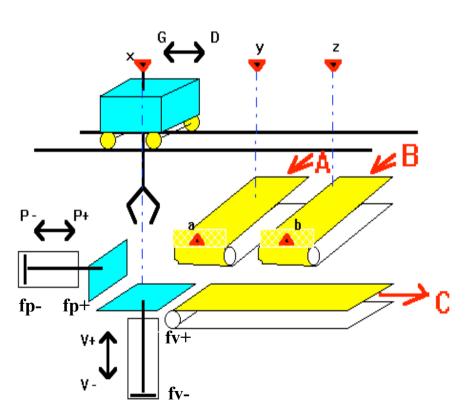

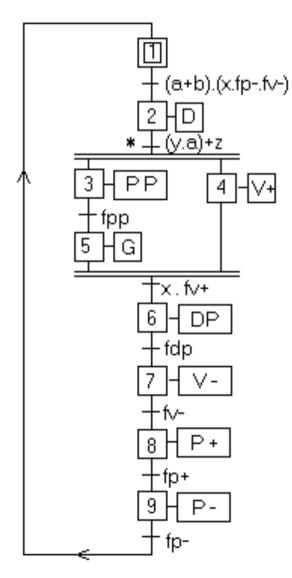

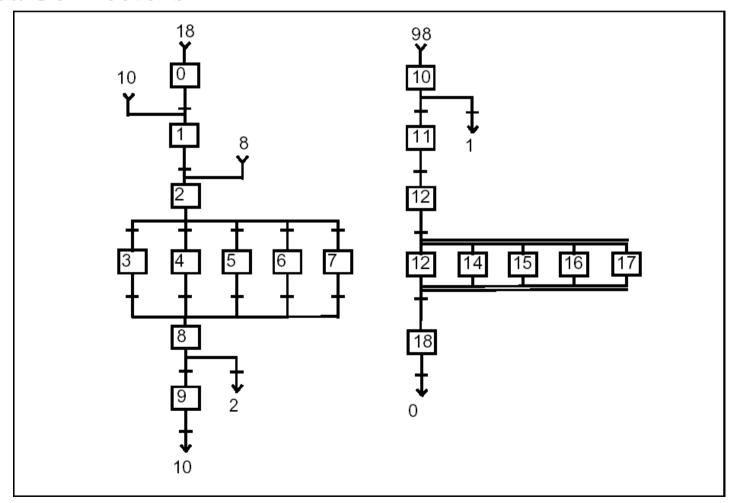

# An Automation Example Solution based on PLCs

#### Example:

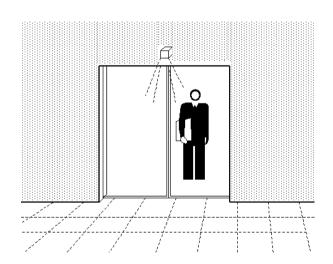

Automation of the Main Entrance Door, in "PLCs Theory," [Omron]

#### Example:

Automation of the Main Entrance Door, in "PLCs Theory," [Omron]

#### **Functional Specifications**

An automatic system that could command the oppening and close of a door is the main purpose of these specifications.

The command operation will be automatic and manual. There must be a selector with two positions in a front pannel of command to select the mode of operation.

The manual mode resorts to the use of two push buttons to open and close the door. Once the OPEN push button is pressed, the door will be openned until the operation is completed, as detected by a limit switch. Upon pushing the CLOSE button the door will be commanded to close, untill the end of the operation is detected by other limit switch.

The automatic mode of operation resorts to the use of two sensors, that detect the proximity of the users. When a person is detected the automatic opening of the door starts. The door remais openned for a period from 5 to 20 seconds, following the null detection if the user. After that period the door starts to close. If during this last phase the presence of other user is detected the close operation is aborted and a new cycle of opening starts.

#### Example:

Automation of the Main Entrance Door, in "PLCs Theory," [Omron]

#### **Technological Specifications**

The proximity sensor that detects the users must be of a model that can be installed over the door (one in the interior and other in the exterior), and must be based on the reflection of infrared radiations, with output by transistor. The sensor sensivity must be tunned such taht its output becomes active if an user is at 2 meters of distance or less.

The motor that activates the open and close of the door must be electrical, three-phasic, ..., etc.

#### **Operating Specifications**

A key must be required to be used in the model of the automatic-manual selector. A counter of the number of operations should be incorporated in the solution, to identify when maintenance is required. The maintenance must be at each 10000 operations, ... etc

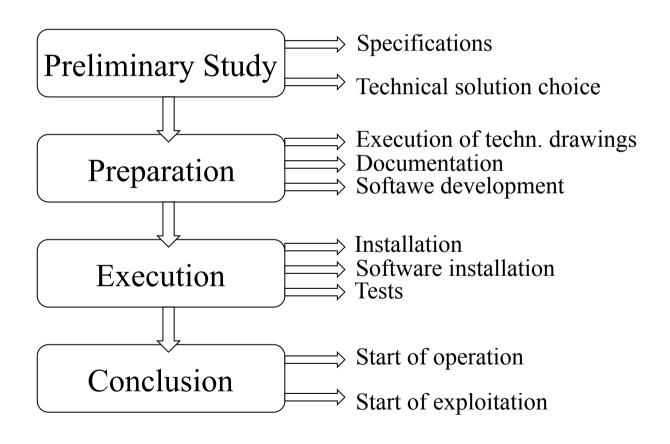

# Phases of a Project in EE&CS: (Automation included)

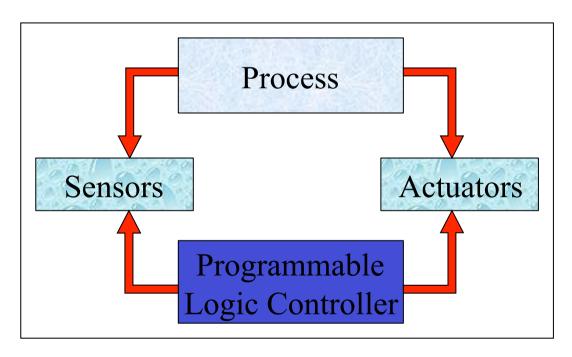

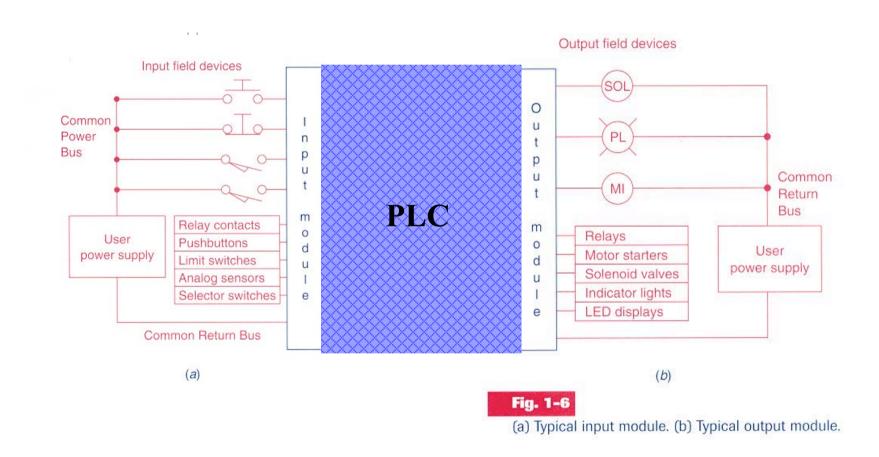

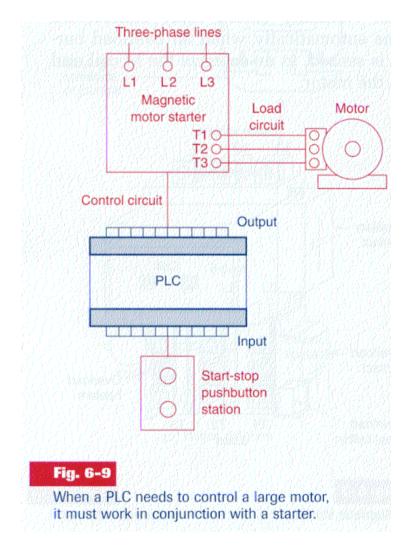

# Automation Problems PLC based solutions

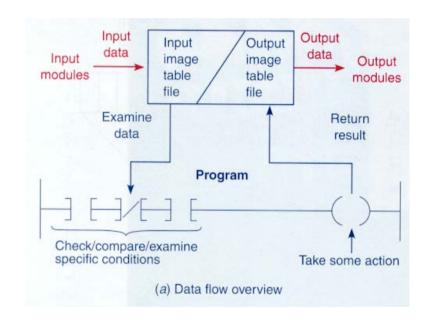

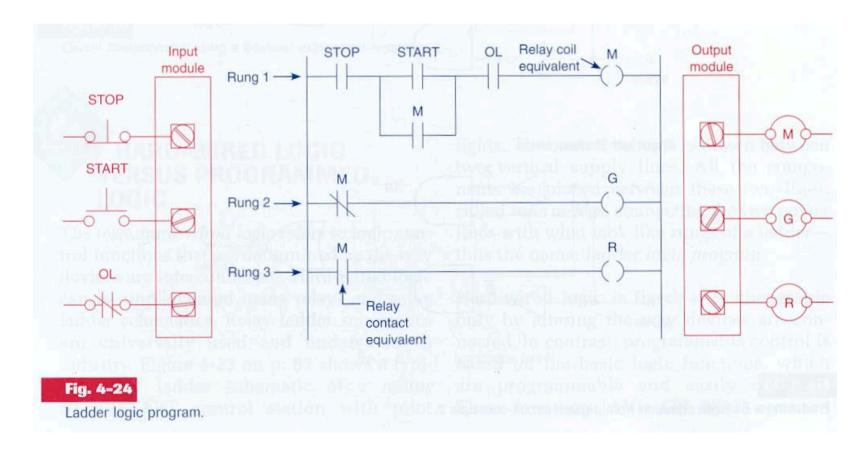

To use PLCS the connection to input devices (for detection and sensing) and to output devices (for command and control) is required.

A software program to implement the proposed solution will be implemented in the PLC.

... and internally, how is it implemented?

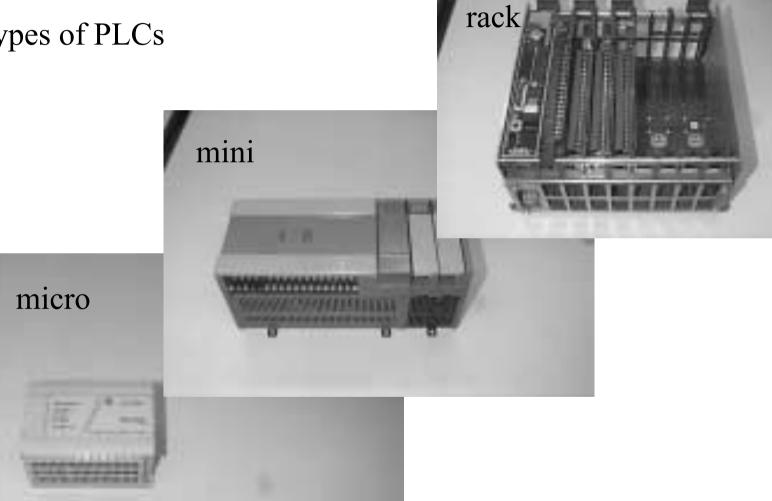

Types of PLCs

P. Oliveira Page 11 API

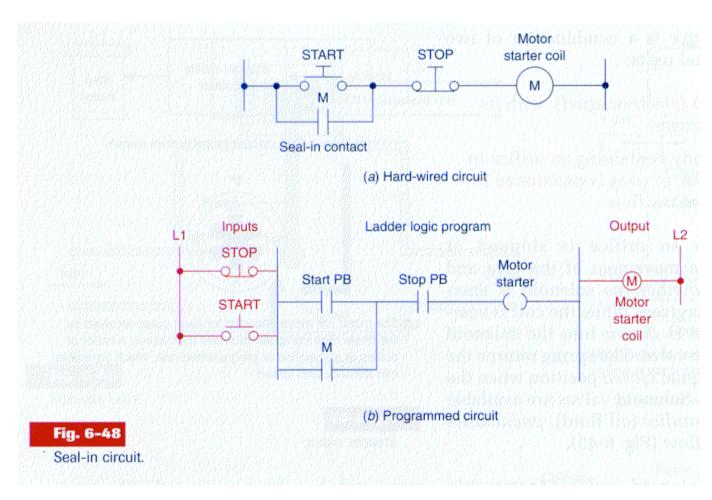

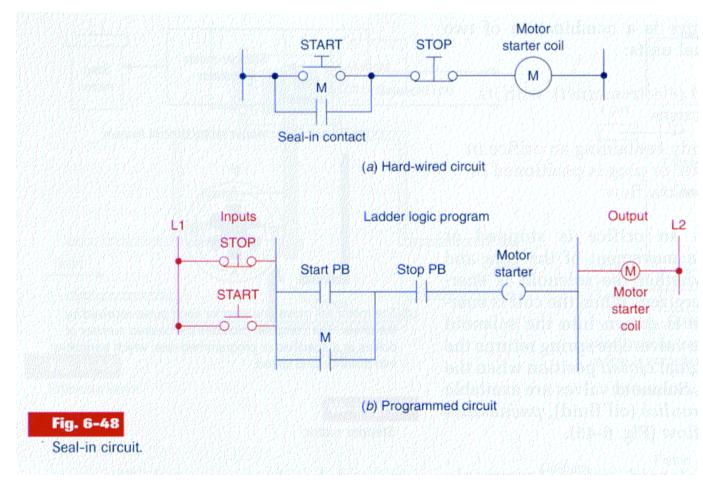

#### Example:

Command of a motor from a console with start and stop buttons.

#### **Internal structure**

#### and

# **Work principles**

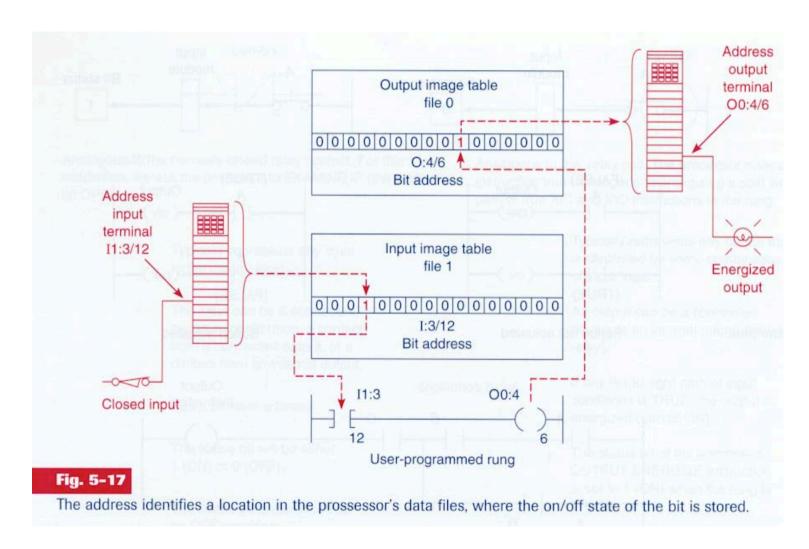

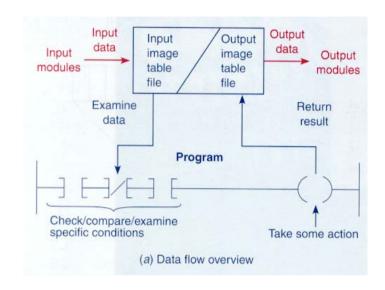

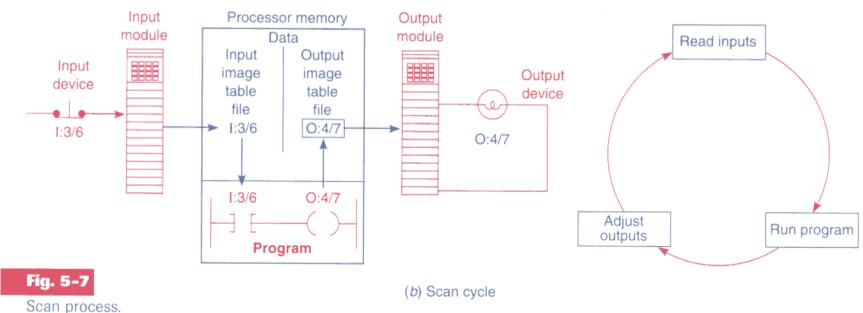

### Internal structure and work principles

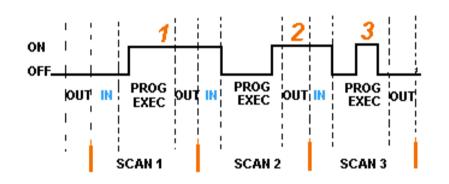

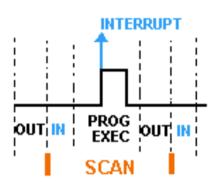

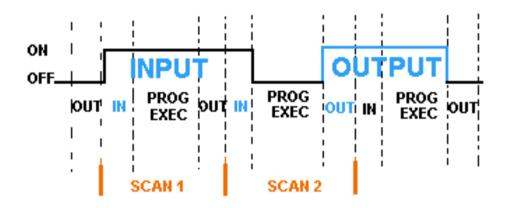

Scan Cycle, Scan Period

The inputs must be actives for at least one scan cycle to have impact (no uncertainty) in the internal PLC state and indirectly in the outputs.

Exception: interrupts...

### Internal structure and work principles

Time interval for an input to have inpact on an output (with probability one)?

#### 2 \* SCAN PERIOD

Smaller time interval (with probability greater than zero) that the change in one input can impact in one output?

SCAN PERIOD - READ TIME - WRITE TIME = EXECUTION TIME

## Internal structure and work principles

Interface for inputs and outputs

Scanning rangs...

Programming using specific devices

OMRON console

video unit (Courtesy of Honeywell, Inc.); (c) personal computer with appropriate software.

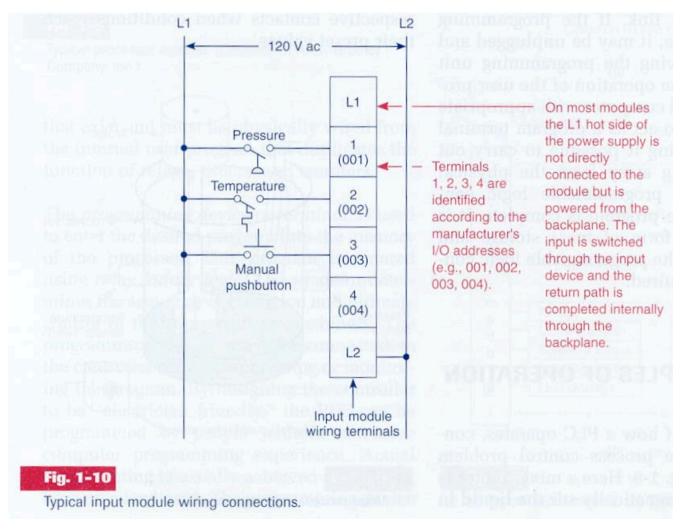

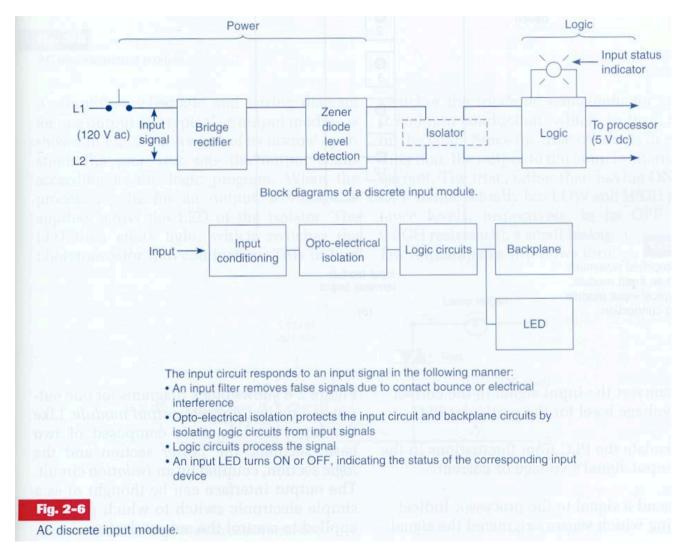

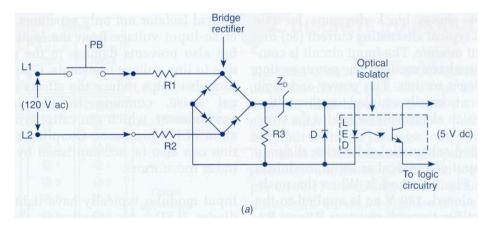

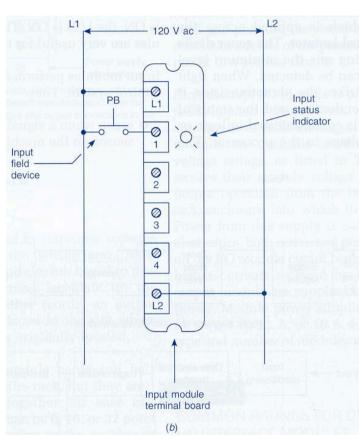

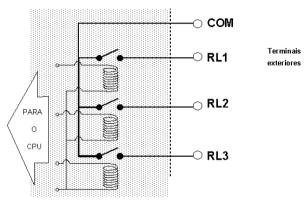

### Input and output interfaces

AC input module (discrete)

# Input and output interfaces

AC input module: simplified implementation

Electronic circuit

Connections to the PLC terminals

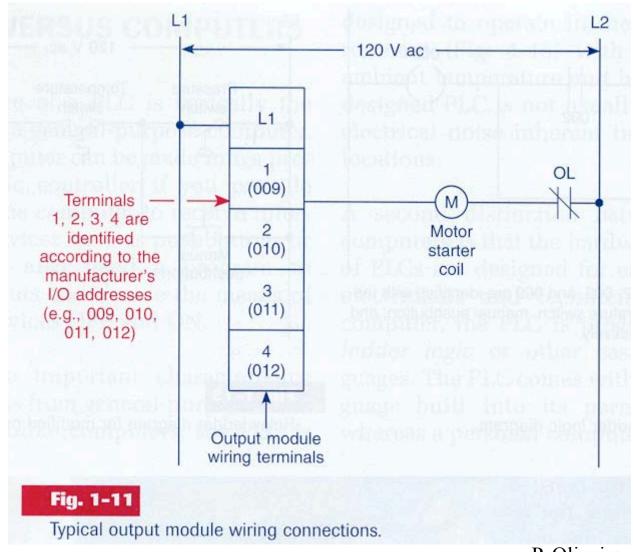

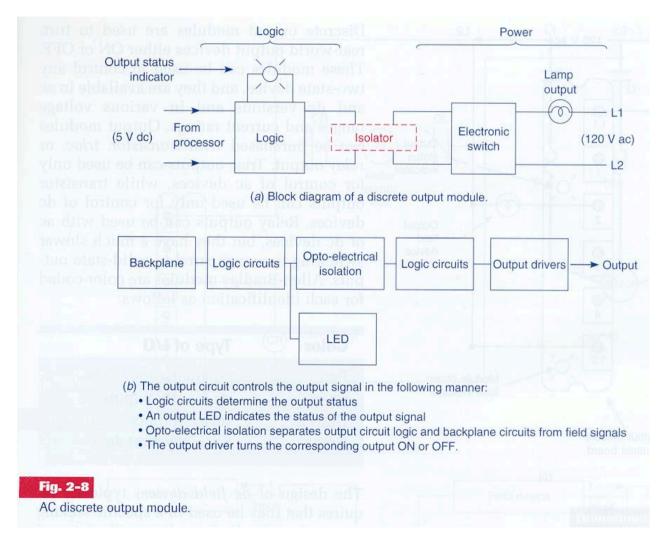

### Input and output interfaces

AC output module (discrete)

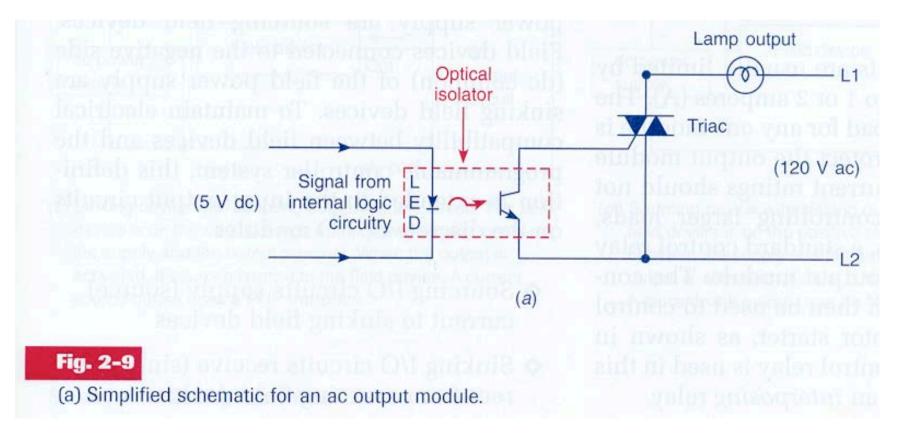

# Input and output interfaces

AC output module (discrete)

Circuito electrónico (simplificado)

# Input and output interfaces

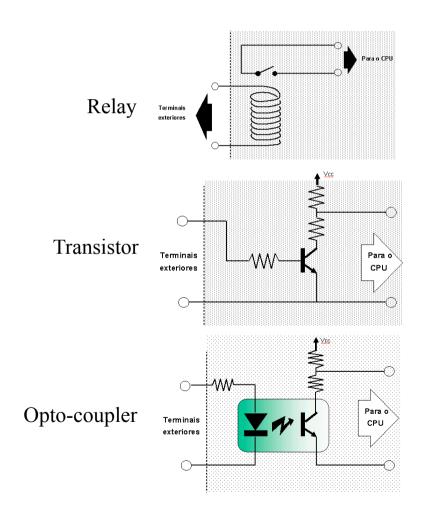

DC input module (discrete)

### Attention to:

- Galvanic isolation

- Economy

- Consumption

- Switching speed

- Noise imunity

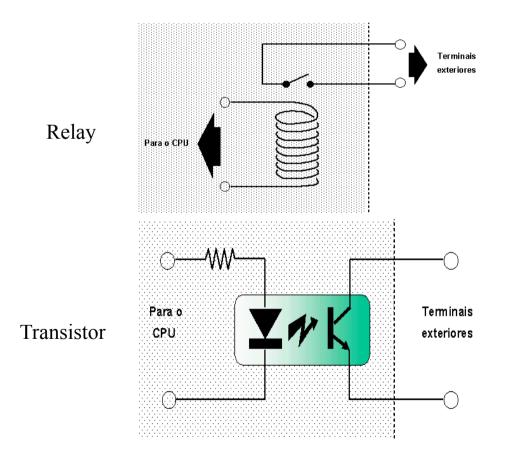

# Input and output interfaces

DC output module (discrete)

Connections to terminals ...

... and protections.

P. Oliveira Page 27

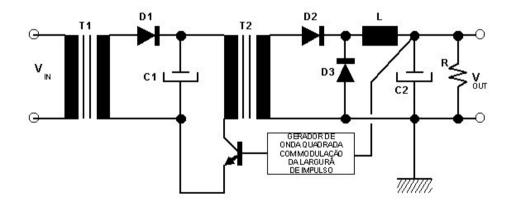

# Components of Programmable Logic Controllers

#### Power sources

#### Attention to:

- Isolation to the noise

- Isolation relative to disturbances on the network

- Efficiency

- Consumption

- Size (volume and weight)

- Robustness relative to load variations

Switching power sources

# **Industrial Automation**

(Automação de Processos Industriais)

# PLCs Programming Languages Instruction List

http://www.isr.ist.utl.pt/~pjcro/courses/api1011/api1011.html

Prof. Paulo Jorge Oliveira pjcro @ isr.ist.utl.pt Tel: 21 8418053 ou 2053 (internal)

# Syllabus:

Chap. 2 – Introduction to PLCs [2 weeks]

•••

Chap. 3 – PLCs Programming Languages [2 weeks]

Standard languages (IEC-1131-3):

Ladder Diagram; Instruction List, and Structured Text.

Software development resources.

•••

Chap. 4 - GRAFCET (Sequential Function Chart) [1 week]

# PLCs Programming Languages (IEC 1131-3)

# Ladder Diagram

### Structured Text

If %I1.0 THEN %Q2.1 := TRUE ELSE %Q2.2 := FALSE END\_IF

## Instruction List

LD %M12 AND %I1.0 ANDN %I1.1 OR %M10 ST %Q2.0

# Sequential Function Chart (GRAFCET)

# Linguagens de programação de PLCs (IEC 1131-3)

# Ladder Diagram

### Structured Text

If %I1.0 THEN %Q2.1 := TRUE ELSE %Q2.2 := FALSE END\_IF

## Instruction List

LD %M12 AND %I1.0 ANDN %I1.1 OR %M10 ST %O2.0

# Sequential Function Chart (GRAFCET)

| ANI1       | Al3        | LDV50 |

|------------|------------|-------|

| <b>A</b> ( | =P9        | =CSW9 |

| Ol2        | NO         | PE    |

| O(         | OM1        |       |

| ANC9       | OI4        |       |

| AQ9        | <b>=Z9</b> |       |

| )          | NO         |       |

| )          | AC9        |       |

| =Q9        | =M1        |       |

|            |            |       |

|            |            |       |

#### **Basic Instructions**

#### **Basic Instructions**

#### **Basic Instructions**

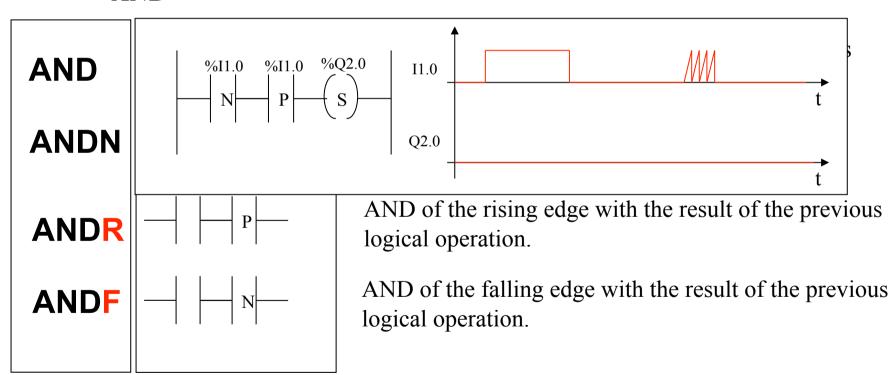

#### AND

# **Instruction list Basic Instructions**

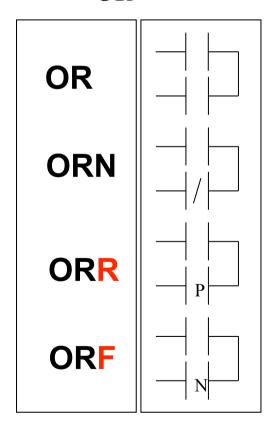

#### OR

OR of the operand with the result of the previous logical operation.

OR of the operand with the inverted result of the previous logical operation.

OR of the rising edge with the result of the previous logical operation.

OR of the falling edge with the result of the previous logical operation.

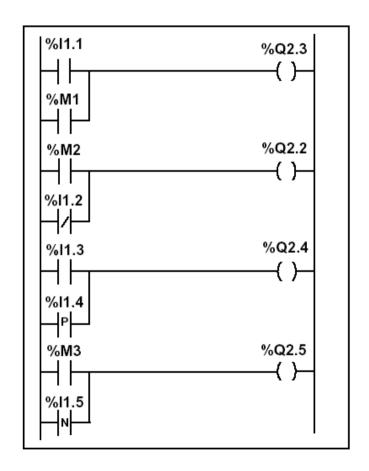

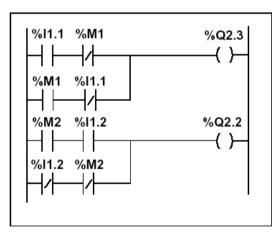

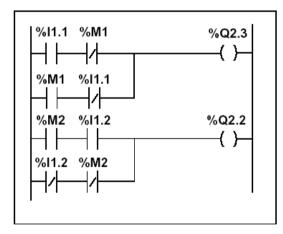

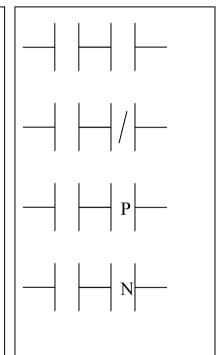

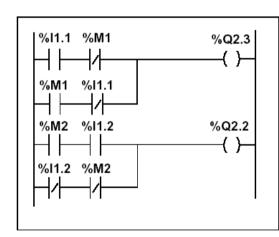

## **Example:**

```

LD %11.1

OR %M1

ST %Q2.3

LD %M2

ORN %11.2

ST %Q2.2

LD %11.3

ORR %11.4

ST %Q2.4

LD %M3

ORF %11.5

ST %Q2.5

```

#### **Basic Instructions**

#### **XOR**

•••

LD %I1.1 XOR %M1 ST %Q2.3

ST %Q2.3 LD %M2

XOR %I1.2 ST %Q2.2

...

| Instruction<br>list | Structured text | Description                                                                                    | Timing diagram                        |

|---------------------|-----------------|------------------------------------------------------------------------------------------------|---------------------------------------|

| XOR                 | XOR             | OR Exclusive between the operand and the previous instruction's Boolean result                 | XOR<br>                               |

| XORN                | XOR (NOT)       | OR Exclusive between the operand inverse and the previous instruction's Boolean result         | XORN<br>  %M2<br>  %I1.2<br>  %Q2.2   |

| XORR                | XOR (RE)        | OR Exclusive between the operand's rising edge and the previous instruction's Boolean result   | XORR<br>  %I1.3<br>  %I1.4<br>  %Q2.4 |

| XORF                | XOR (FE)        | OR Exclusive between the operand's falling edge and the previous instruction's Boolean result. | XORF<br>%M3<br>%l1.5<br>%Q2.5         |

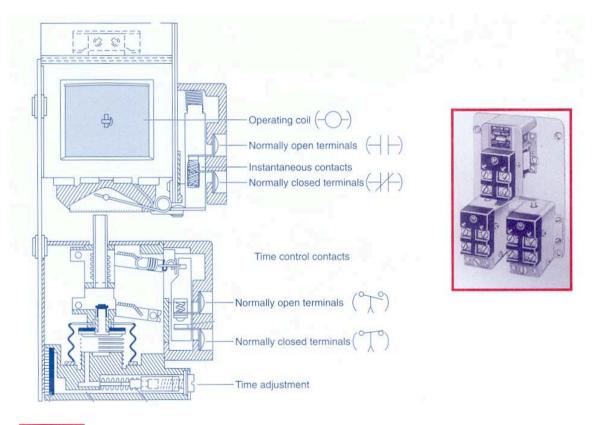

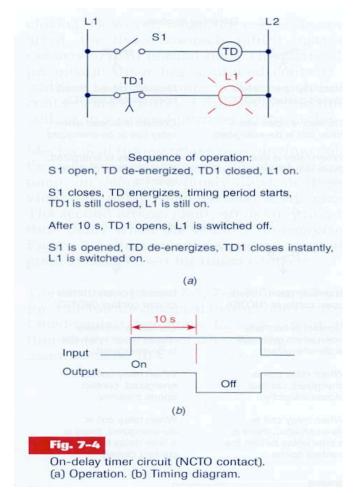

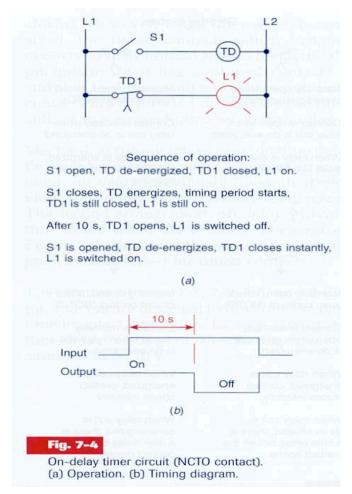

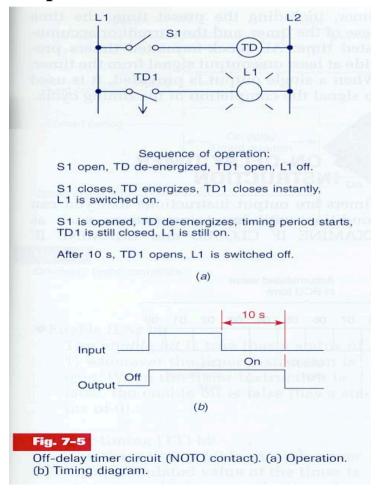

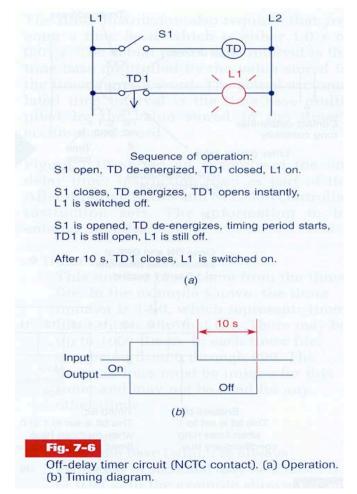

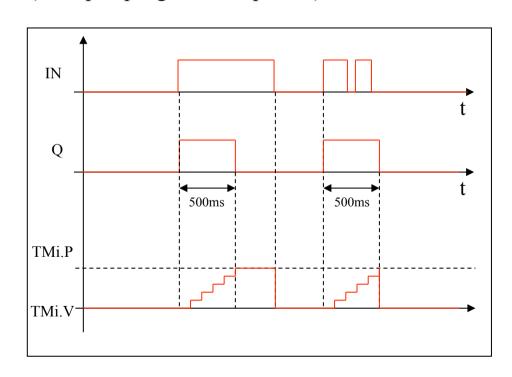

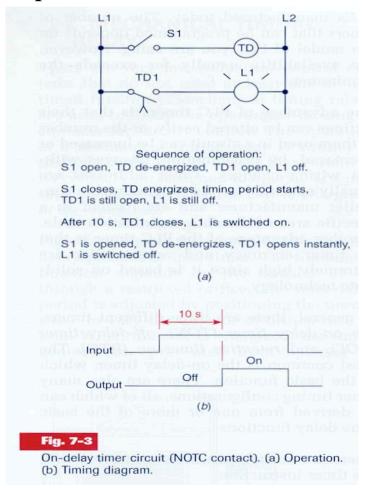

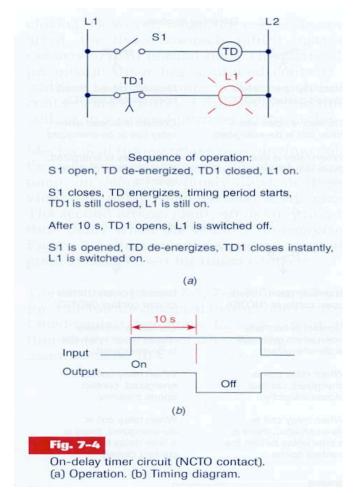

# Temporized Relays

or

## **Timers**

Fig. 7-1

Pneumatic on-delay timer. (Courtesy of Allen-Bradley Company, Inc.)

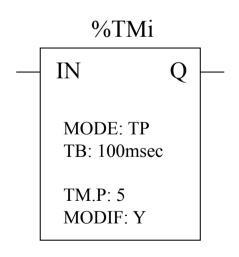

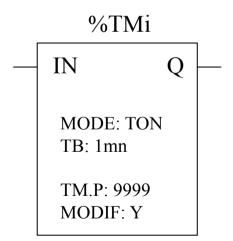

# Temporized Relays

or

#### **Timers**

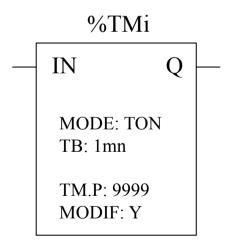

%TMi

IN Q

MODE: TON

TB: 1mn

TM.P: 9999

MODIF: Y

### Characteristics:

Identifier:%TMi 0..63 in the TSX37

Input: IN to activate

Mode: TON On delay

TOFF Off delay

TP Monostable

Time basis: TB 1mn (def.), 1s,

100ms, 10ms

Programmed value: %TMi.P 0...9999 (def.)

period=TB\*TMi.P

Actual value: %TMi.V 0...TMi.P

(can be real or tested)

Modifiable: Y/N can be modified from

the console

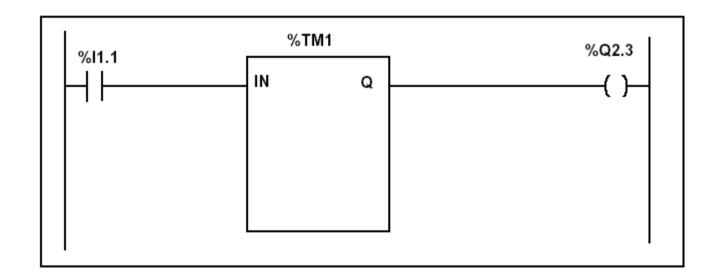

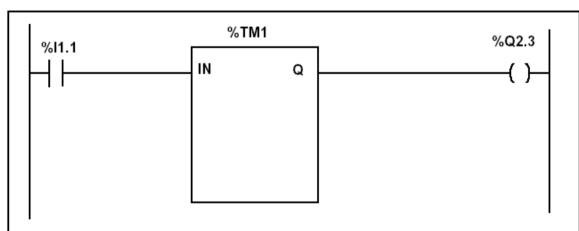

# Relés temporizados Ou Timers

```

LD %I1.1

IN %TM1

LD %TM1.Q

ST %Q2.3

```

#### **Example:**

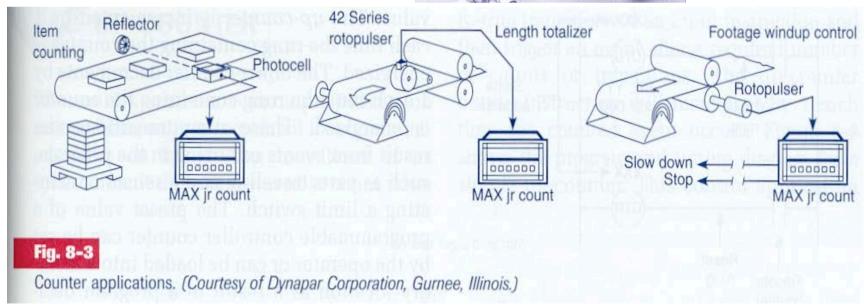

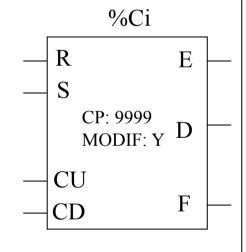

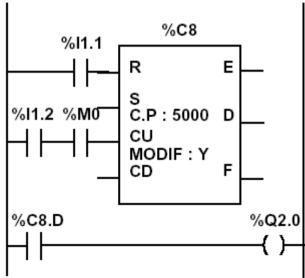

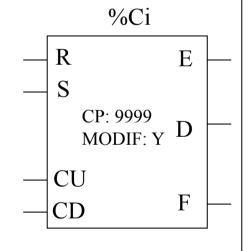

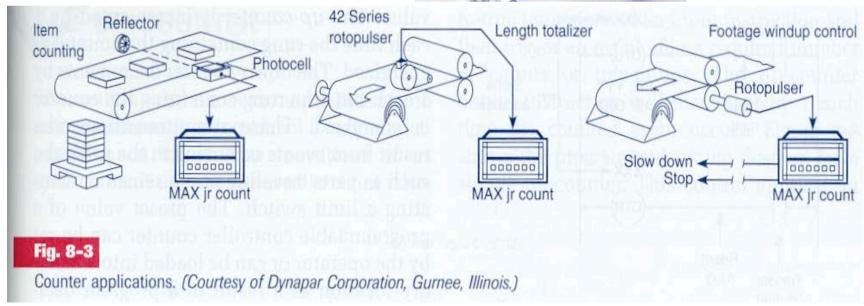

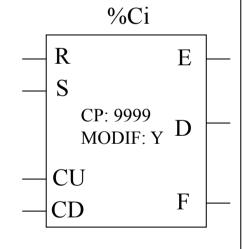

#### **Counters**

Some applications...

#### **Counters**

#### Characteristics:

Identifier:%Ci 0..31 in the TSX37

Value progr.: %Ci.P 0...9999 (def.)

Value Actual: %Ci.V 0...Ci.P (only to be read)

Modifiable: Y/N can be modified from

the console

Inputs: R Reset Ci.V=0

S Preset Ci.V=Ci.P

CU Count Up

CD Count Down

Outputs: E Overrun %Ci.E=1 %Ci.V=0->9999

D Done %Ci.D=1 %Ci.V=Ci.P

F Full %Ci.F=1 %Ci.V=9999->0

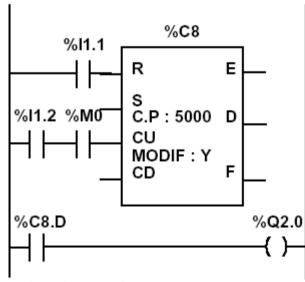

### **Counters**

#### **Example:**

#### Instruction list language

LD %I1.1

R %C8

LD %I1.2

AND %M0

CU %C8

LD %C8.D

ST %Q2.0

## **Numerical Processing**

### **Algebraic and Logic Functions**

```

LD [%MW50>10]

ST %Q2.2

LD %I1.0

[%MW10:=%KW0+10]

LDF %I1.2

[INC%MW100]

```

## **Numerical Processing**

#### **Arithmetic Functions**

| +   | addition of two operands                                  | SQRT | square root of an operand    |

|-----|-----------------------------------------------------------|------|------------------------------|

| -   | subtraction of two operands                               | INC  | incrementation of an operand |

| *   | multiplication of two operands                            | DEC  | decrementation of an operand |

| 1   | division of two operands ABS absolute value of an operand |      | absolute value of an operand |

| REM | remainder from the division of 2 operands                 |      |                              |

#### Operands

| Туре                       | Operand 1 (Op1)  | Operand 2 (Op2)                              |

|----------------------------|------------------|----------------------------------------------|

| Indexable words            | %MW              | %MW,%KW,%Xi.T                                |

| Non-indexable words        | %QW,%SW,%NW,%BLK | Imm.Val.,%IW,%QW,%SW,%NW,<br>%BLK, Num.expr. |

| Indexable double words     | %MD              | %MD,%KD                                      |

| Non-indexable double words | %QD,%SD          | Imm.Val.,%ID,%QD,%SD, Numeric expr.          |

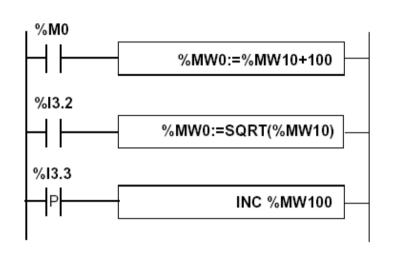

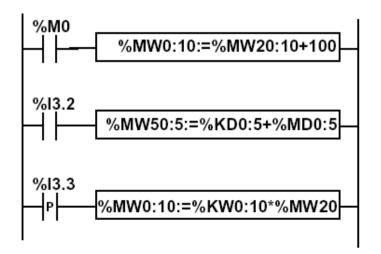

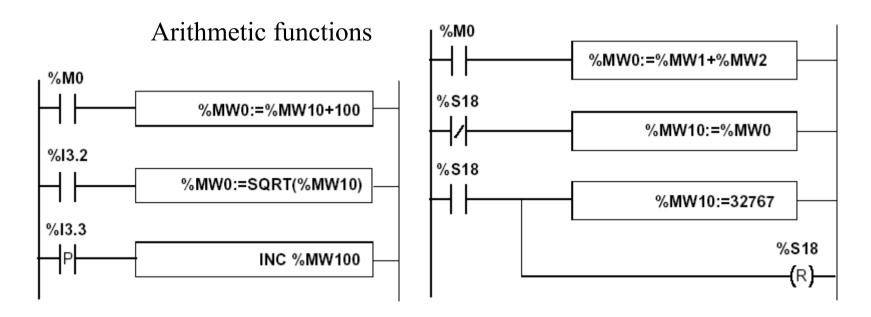

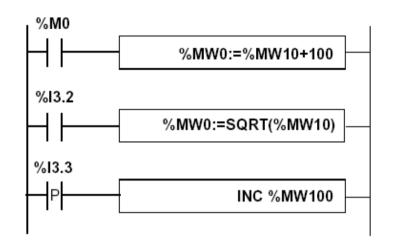

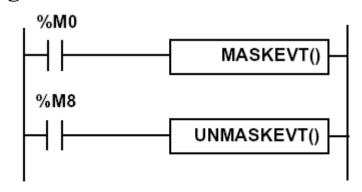

## **Numerical Processing**

### **Example:**

Arithmetic functions

#### Instruction list language

```

LD %M0

[%MW0:=%MW10+100]

LD %I3.2

[%MW0:=SQRT(%MW10)]

LD %I3.3

[INC %MW100]

```

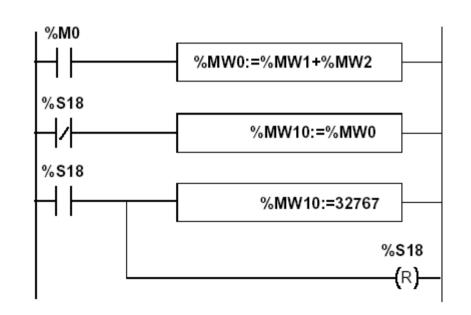

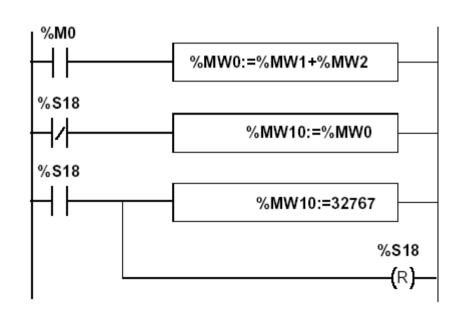

## **Numerical Processing**

**Example:**

Arithmetic functions

#### Example in instruction list language:

```

LD %M0

[%MW0:=%MW1+%MW2]

LDN %S18

[%MW10:=%MW0]

LD %S18

[%MW10:=32767]

R %S18]

```

Use of a system variable:

%S18 – flag de overflow

### **Numerical Processing**

#### **Logic Functions**

| AND | AND (bit by bit) between two operands          |  |  |

|-----|------------------------------------------------|--|--|

| OR  | logical OR (bit by bit) between two operands   |  |  |

| XOR | exclusive OR (bit by bit) between two operands |  |  |

| NOT | logical complement (bit by bit) of an operand  |  |  |

Comparison instructions are used to compare two operands.

- >: tests whether operand 1 is greater than operand 2,

- >=: tests whether operand 1 is greater than or equal to operand 2,

- <: tests whether operand 1 is less than operand 2,</li>

- <=: tests whether operand 1 is less than or equal to operand 2,

- =: tests whether operand 1 is different from operand 2.

#### Operands

| Туре                       | Operands 1 and 2 (Op1 and Op2)               |

|----------------------------|----------------------------------------------|

| Indexable words            | %MW,%KW,%Xi.T                                |

| Non-indexable words        | lmm.val.,%IW,%QW,%SW,%NW,%BLK, Numeric Expr. |

| Indexable double words     | %MD,%KD                                      |

| Non-indexable double words | lmm.val.,%ID,%QD,%SD,Numeric expr.           |

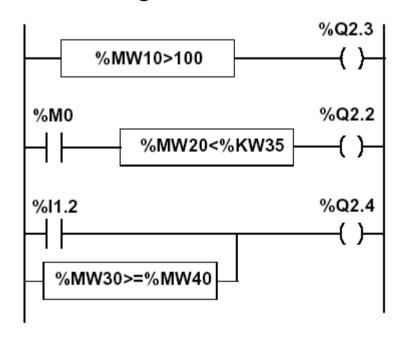

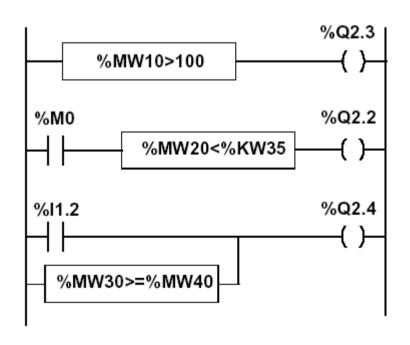

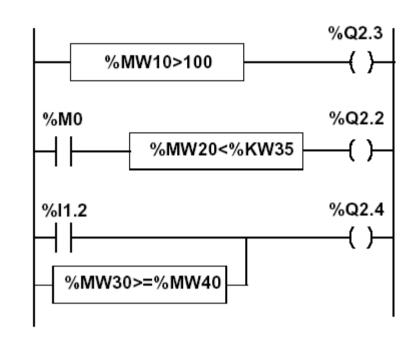

#### **Numerical Processing**

### **Example:**

### Logic functions

#### Instruction list language

LD [%MW10>100]

ST %Q2.3

LD %M0

AND [%MW20<%KW35]

ST %Q2.2

LD %I1.2

OR [%MW30>=%MW40]

ST %Q2.4

## **Numerical Processing**

## Priorities on the execution of the operations

| Rank | Instruction               |

|------|---------------------------|

| 1    | Instruction to an operand |

| 2    | *,/,REM                   |

| 3    | +,-                       |

| 4    | <,>,<=,>=                 |

| 5    | =,<>                      |

| 6    | AND                       |

| 7    | XOR                       |

| 8    | OR                        |

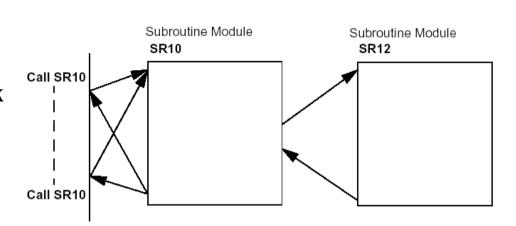

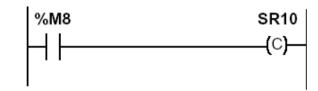

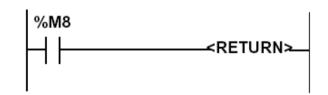

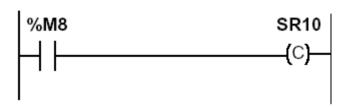

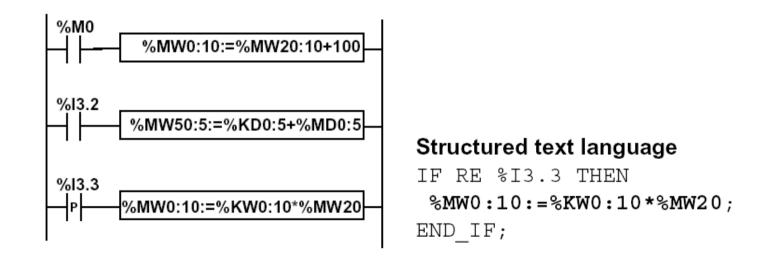

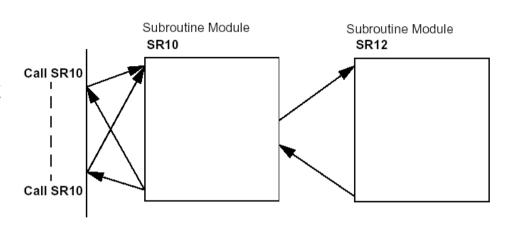

#### **Structures for Control of Flux**

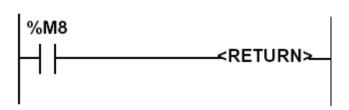

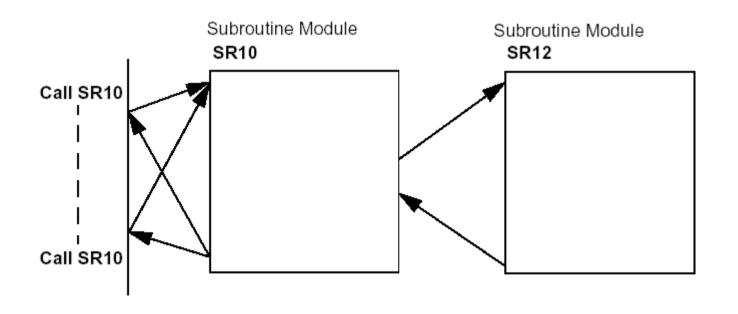

#### **Subroutines**

#### Call and Return

#### Ladder language:

#### Instruction list language:

LD %M8 SR10

#### Ladder language

#### Instruction list language

LD %M8

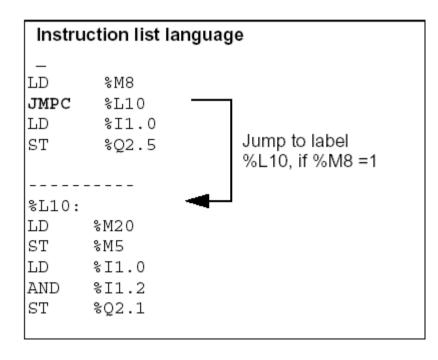

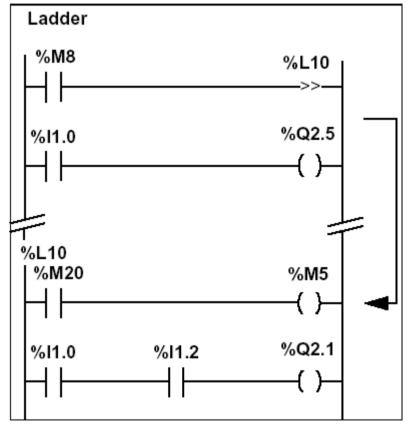

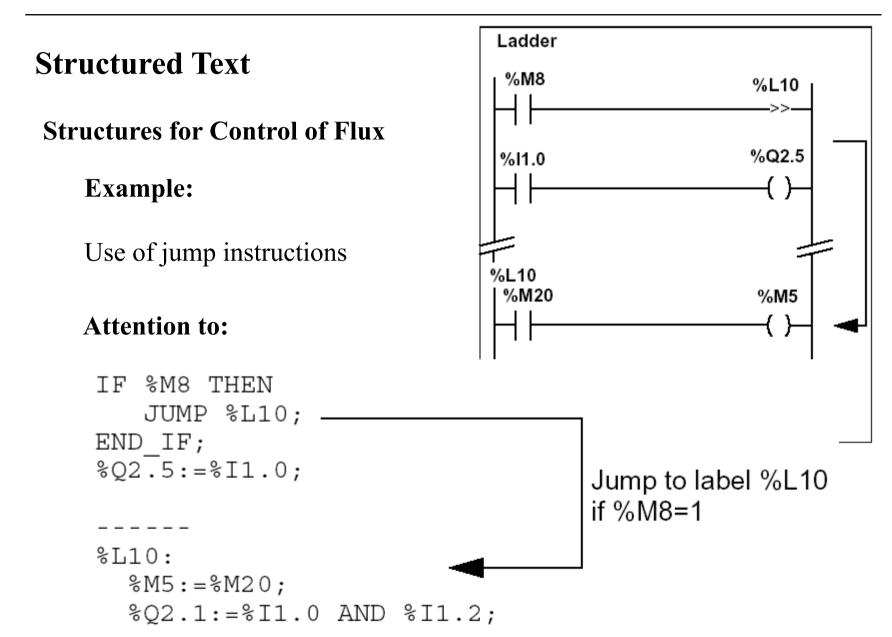

#### **Structures for Control of Flux**

#### **JUMP instructions:**

#### Conditional and unconditional

Jump instructions are used to go to a programming line with an %Li label address:

- JMP: unconditional program jump

- JMPC: program jump if the instruction's Boolean result from the previous test is set at 1

- JMPCN: program jump if the instruction's Boolean result from the previous test is set at 0. %Li is the label of the line to which the jump has been made (address i from 1 to 999 with maximum 256 labels)

#### **Structures for Control of Flux**

### **Example:**

Use of jump instructions

#### **Structures for Control of Flux**

#### Halt

Stops all processes!

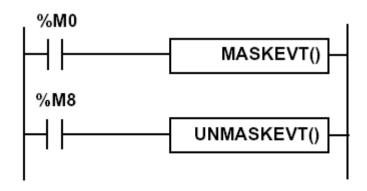

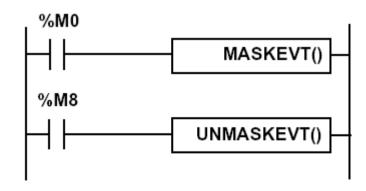

## **Events masking**

### There are other advanced instrauctions (see manual)

- Monostable

- Registers of 256 words (LIFO ou FIFO)

- DRUMs

- Comparators

- Shift-registers

•••

- Functions to manipulate *floats*

- Functions to convert bases and types

#### **Numerical Tables**

| Туре           | Format         | Maximum<br>address | Size            | Write access |

|----------------|----------------|--------------------|-----------------|--------------|

| Internal words | Simple length  | %MWi:L             | i+L<=Nmax (1)   | Yes          |

|                | Double length  | %MWDi:L            | i+L<=Nmax-1 (1) | Yes          |

|                | Floating point | %MFi:L             | i+L<=Nmax-1 (1) | Yes          |

| Constant words | Single length  | %KWi:L             | i+L<=Nmax (1)   | No           |

|                | Double length  | %KWDi:L            | i+L<=Nmax-1 (1) | No           |

|                | Floating point | %KFi:L             | i+L<=Nmax-1 (1) | No           |

| System word    | Single length  | %SW50:4 (2)        | -               | Yes          |

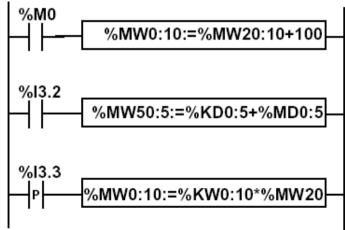

#### Instruction list language

LD %M0 [%MW0:10:=%MW20:10+100]

LD %I3.2

[%MD50:5:=%KD0:5+%MD0:5]

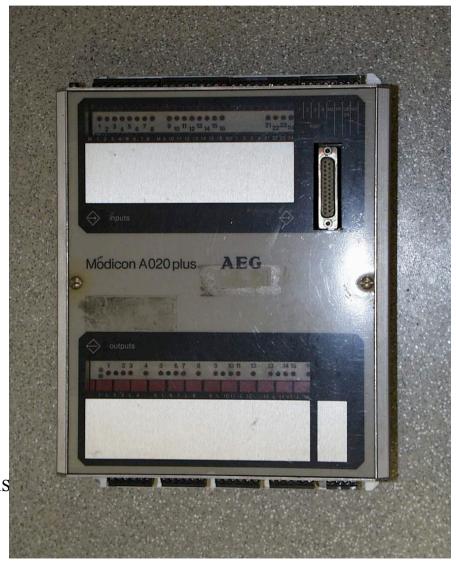

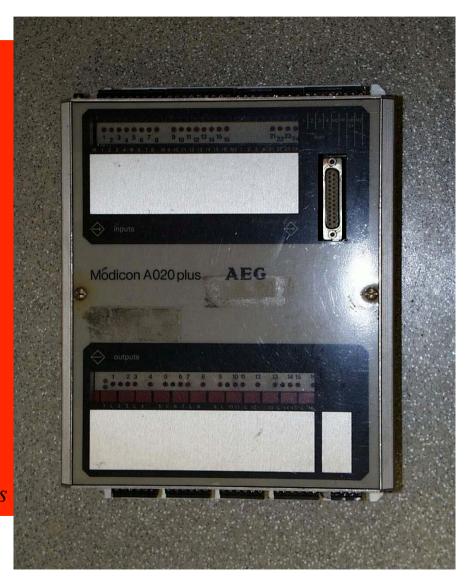

# DOLOG80

#### PLC AEG A020 Plus:

#### **Inputs:**

- 20 binary with opto-couplers

- 4 analogs (8 bits, 0-10V)

#### **Outputs:**

- 16 binary with relays of 2A

- 1 analogs (8 bits, 0-10V)

Interface for progr.: RS232

#### **Processador:**

- 8031

- 2 Kbytes de RAM

- 2 Kbytes EEPROM => 896 instructions

- Average cycle time: 6.5 ms

### PLC AEG A020 Plus

# DOLOG80

#### **OPERANDS**

• I1 to I20 Binary inputs

• Q1 to Q16 Bynary outputs

• M1 to M128 Auxiliary memory

• T1 to T8 Timers (base 100ms)

• T9 to T16 Timers (base 25ms)

• C1 to C16 Contadores with 16 bits

### Chap. 3 – Old PLCs

# DOLOG80 (cont.)

# **Example:**

| AI1        | AI3            | LDV50 |

|------------|----------------|-------|

| <b>A</b> ( | <b>=P9</b>     | =CSW  |

| OI2        | NO             | PE    |

| <b>O</b> ( | OM1            |       |

| ANC9       | OI4            |       |

| AQ9        | $=\mathbb{Z}9$ |       |

| )          | NO             |       |

| )          | AC9            |       |

|            |                |       |

=M1

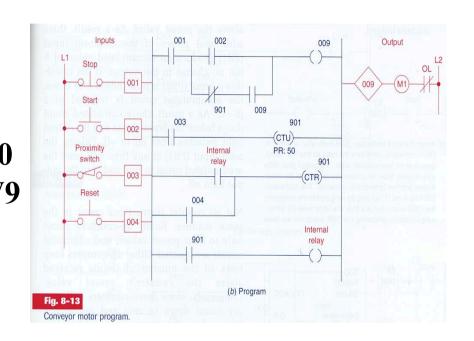

Legend: Stop = I1 Start = I2Proximity Sensor = I3 Reset = I4Counter= C9  $Internal\ relay = M1$ Motor = Q9

# **Industrial Automation**

(Automação de Processos Industriais)

# PLCs Programming Languages Ladder Diagram

http://www.isr.ist.utl.pt/~pjcro/courses/api0910/api0910.html

Prof. Paulo Jorge Oliveira pjcro @ isr.ist.utl.pt Tel: 21 8418053 ou 2053 (internal)

# Syllabus:

Chap. 2 – Introduction to PLCs [2 weeks]

•••

Chap. 3 – PLCs Programming Languages [2 weeks]

Standard languages (IEC-1131-3):

Ladder Diagram; Instruction List, and Structured Text. Software development resources.

•••

Chap. 4 - GRAFCET (Sequential Function Chart) [1 week]

# PLCs Programming Languages (IEC 1131-3)

### Ladder Diagram

### Structured Text

If %I1.0 THEN %Q2.1 := TRUE ELSE %Q2.2 := FALSE END\_IF

### Instruction List

LD %M12 AND %I1.0 ANDN %I1.1 OR %M10 ST %Q2.0

# Sequential Function Chart (GRAFCET)

# Linguagens de programação de PLCs (IEC 1131-3)

### Ladder Diagram

### Structured Text

If %I1.0 THEN %Q2.1 := TRUE ELSE %Q2.2 := FALSE END\_IF

### Instruction List

LD %M12 AND %I1.0 ANDN %I1.1 OR %M10 ST %Q2.0

# Sequential Function Chart (GRAFCET)

# **Types of operands:**

| Bits                                 | Description                                                                                                                                                                                                                                                       | Examples         | Write<br>access                          |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------|

| Immediate<br>values                  | 0 or 1 (False or True)                                                                                                                                                                                                                                            | 0                | _                                        |

| Inputs/outputs                       | These bits are the "logic images" of the electrical states of the inputs/outputs. They are stored in the data memory and updated each time the task in which they are configured is polled.  Note: The unused input/output bits may not be used as internal bits. | %I23.5<br>%Q51,2 | No<br>Yes                                |

| Internal                             | The internal bits are used to store the intermediary states during execution of the program.                                                                                                                                                                      | %M200            | Yes                                      |

| System                               | The system bits %S0 to %S127 monitor the correct operation of the PLC and the running of the application program.                                                                                                                                                 | %S10             | Accordin<br>g to i                       |

| Function<br>blocks                   | The function block bits correspond to the outputs of the function blocks or DFB instance.  These outputs may be either directly connected or used as an object.                                                                                                   | %TM8.Q           | No                                       |

| Word extracts                        | With the PL7 software it is possible to extract one of the 16 bits of a word object.                                                                                                                                                                              | %MW10:X5         | Accordin<br>g to the<br>type of<br>words |

| Grafcet steps<br>and macro-<br>steps | The Grafcet status bits of the steps, macro-steps and macro-step steps are used to recognize the Grafcet status of step i, of macro-step j or of step i of the macro-step j.                                                                                      | %X21<br>%X5.9    | Yes<br>Yes                               |

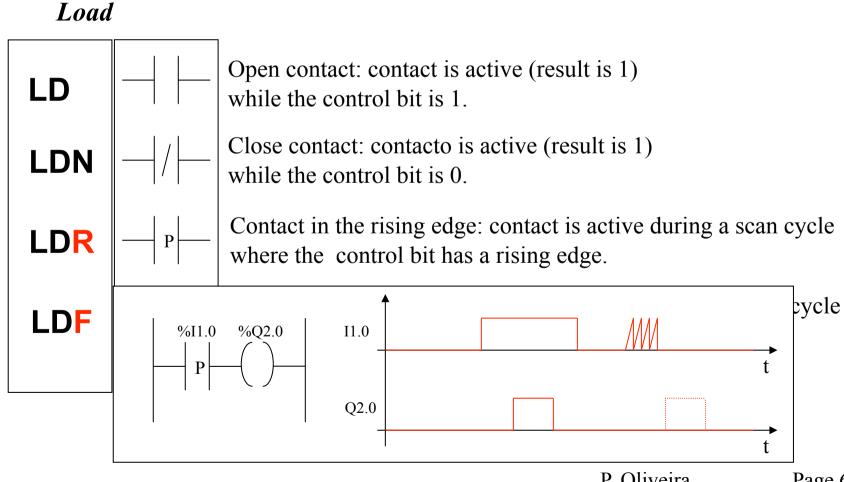

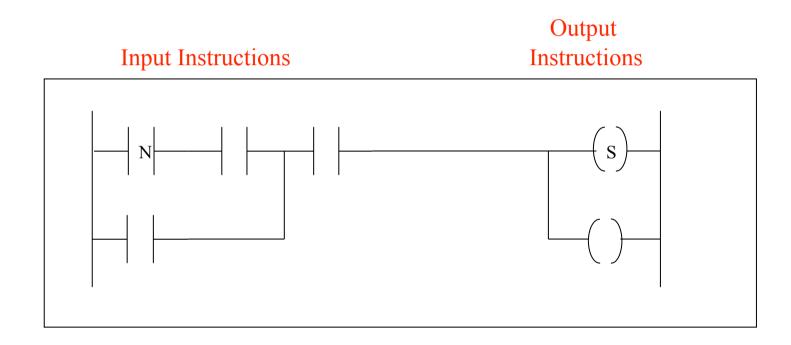

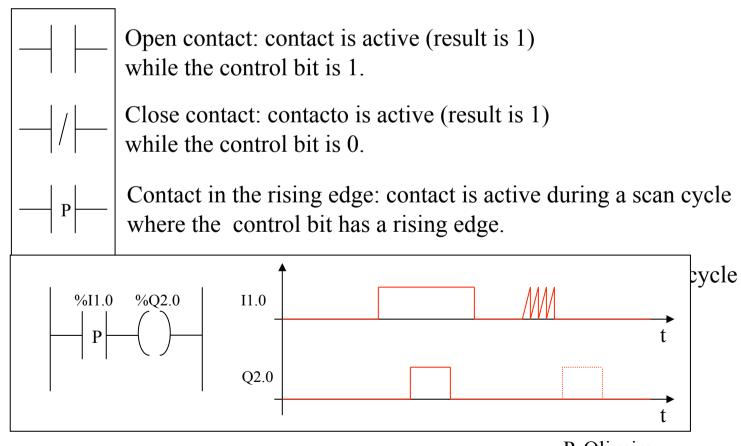

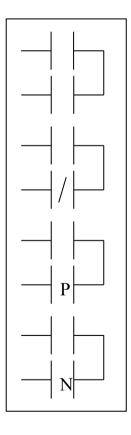

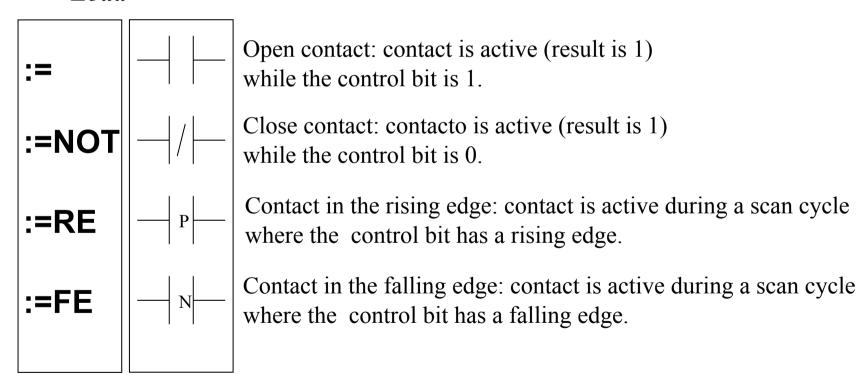

### **Basic Instructions**

#### Load

# **Ladder diagram Basic Instructions**

### Load operands

# Permitted operands

The following table gives a list of the operands used for these instructions.

| Ladder                 | Instruction list | Structured text | Operands                                                                             |

|------------------------|------------------|-----------------|--------------------------------------------------------------------------------------|

| $\neg \vdash$          | LD               | :=              | %I,%Q,%M,%S,%BLK,%•:Xk, %Xi, (True and False in instruction list or structured text) |

| $\neg \vdash$          | LDN              | :=NOT           | %I,%Q,%M,%S,%BLK,%•:Xk, %Xi, (True and False in instruction list or structured text) |

| — P —                  | LDR              | :=RE            | %I,%Q,%M                                                                             |

| <b>−</b>   <b>ν</b>  − | LDF              | :=FE            | %I,%Q,%M                                                                             |

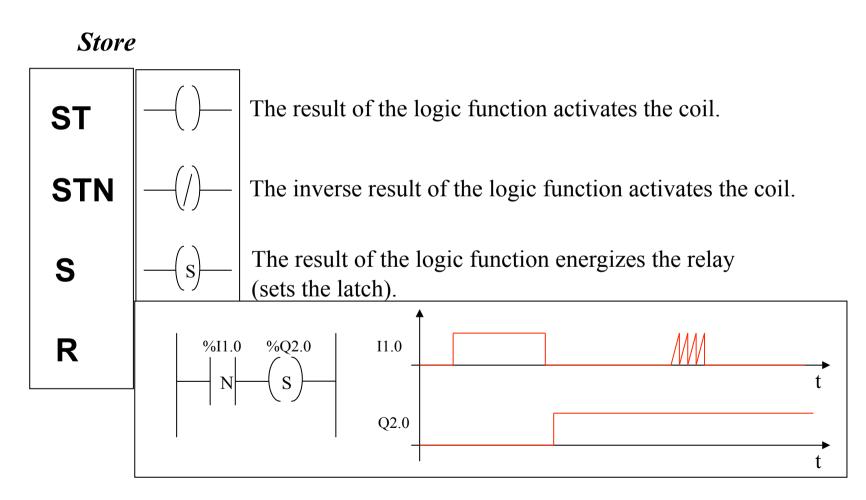

### **Basic Instructions**

#### Store

The result of the logic function activates the coil.

—(/)— The inverse result of the logic function activates the coil.

\_\_(s)\_\_\_ The result of the logic function energizes the relay (sets the latch).

# **Ladder diagram Basic Instructions**

### **Store** operands

# Permitted operands

The following table gives a list of the operands used for these instructions

| Language<br>data | Instruction list | Structured text | Operands                                                  |

|------------------|------------------|-----------------|-----------------------------------------------------------|

| <del>-( )-</del> | ST               | :=              | %I,%Q,%M,%S,%•:Xk                                         |

| -(/)-            | STN              | :=NOT           | %I,%Q,%M,%S,%•:Xk                                         |

| _(s)_            | S                | SET             | %I,%Q,%M,%S,%•:Xk,%Xi Only in the preliminary processing. |

| -                | R                | RESET           | %I,%Q,%M,%S,%•:Xk,%Xi Only in the preliminary processing. |

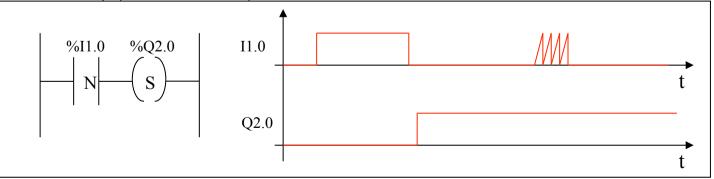

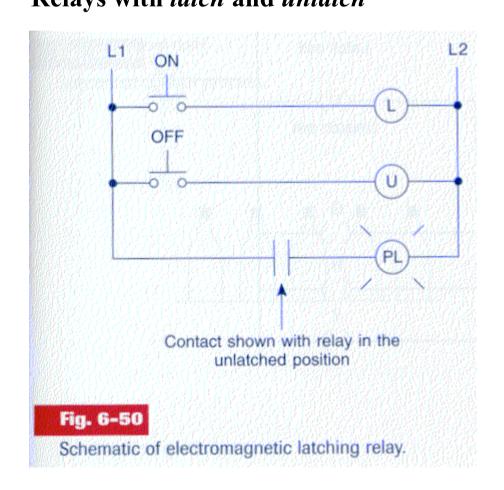

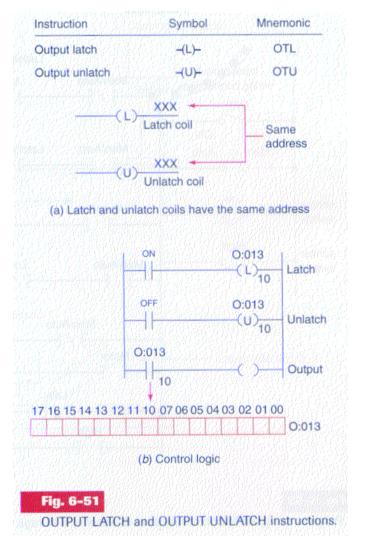

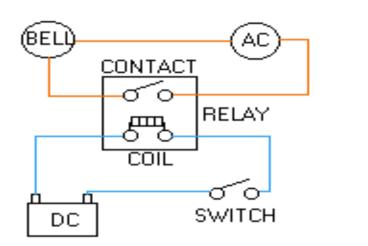

# Allen Bradley notation Relays with latch and unlatch

**Relay-type instructions**

Example:

### **Basic Instructions**

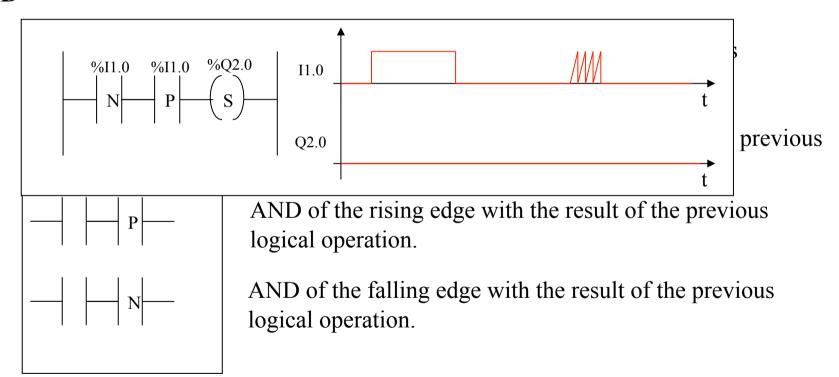

#### **AND**

### **Basic Instructions**

#### OR

OR of the operand with the result of the previous logical operation.

OR of the operand with the inverted result of the previous logical operation.

OR of the rising edge with the result of the previous logical operation.

OR of the falling edge with the result of the previous logical operation.

### **Basic Instructions**

**XOR**

| Instruction<br>list | Structured text | Description                                                                                    | Timing diagram                      |

|---------------------|-----------------|------------------------------------------------------------------------------------------------|-------------------------------------|

| XOR                 | XOR             | OR Exclusive between the operand and the previous instruction's Boolean result                 | XOR<br>                             |

| XORN                | XOR (NOT)       | OR Exclusive between the operand inverse and the previous instruction's Boolean result         | XORN<br>%M2<br>%I1.2<br>%Q2.2       |

| XORR                | XOR (RE)        | OR Exclusive between the operand's rising edge and the previous instruction's Boolean result   | XORR<br>%I1.3<br>%I1.4<br>%Q2.4     |

| XORF                | XOR (FE)        | OR Exclusive between the operand's falling edge and the previous instruction's Boolean result. | XORF<br>  %M3<br>  %I1.5<br>  %Q2.5 |

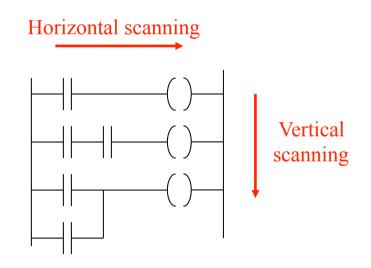

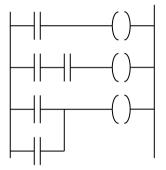

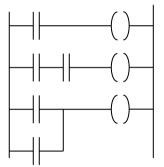

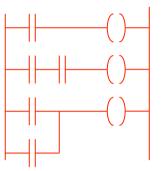

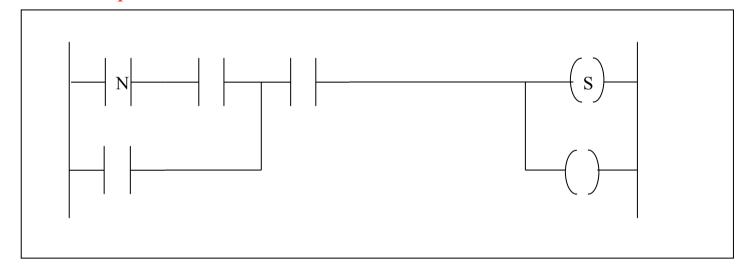

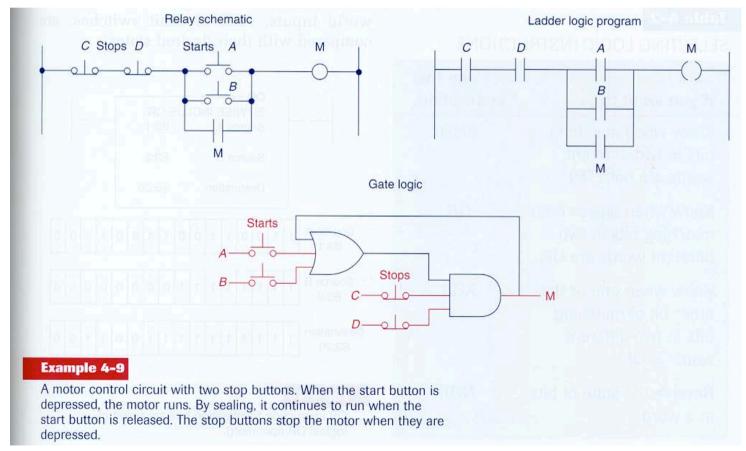

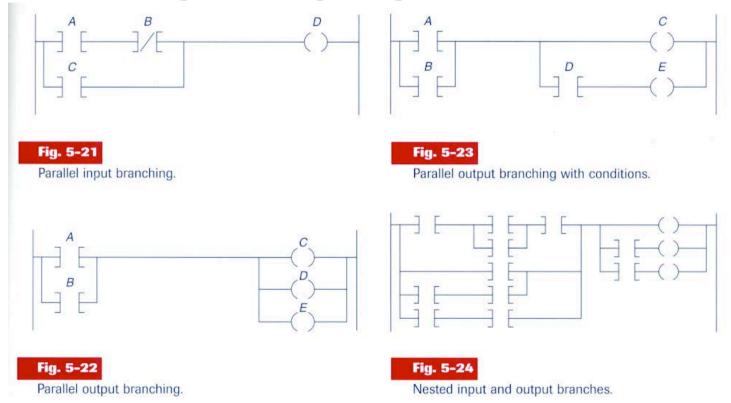

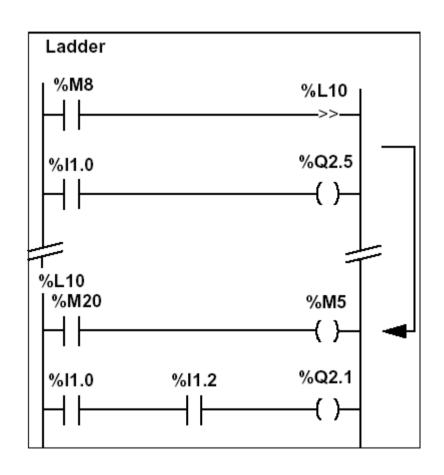

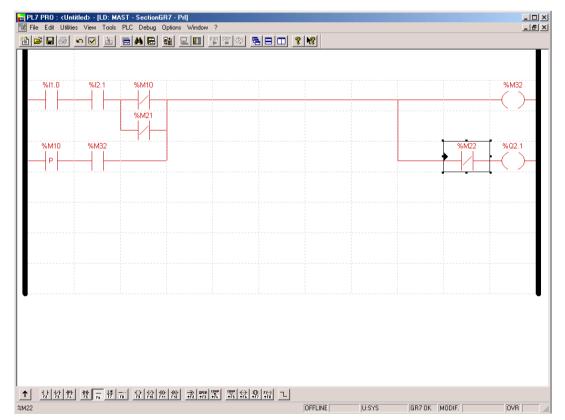

### Ladder assembling

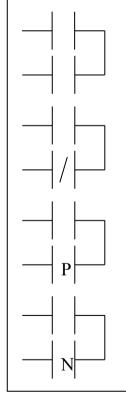

# Input Instructions

# Output Instructions

The outputs that have a TRUE logical function, evaluated from the left to right and from the top to the bottom, are energized (Schneider, Micro PLCs).

### **Example:**

### **Example:**

### **Example:**

### **Example:**

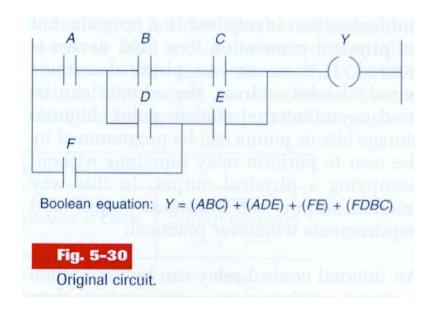

General case of Inputs and Outputs in parallel, with derivations

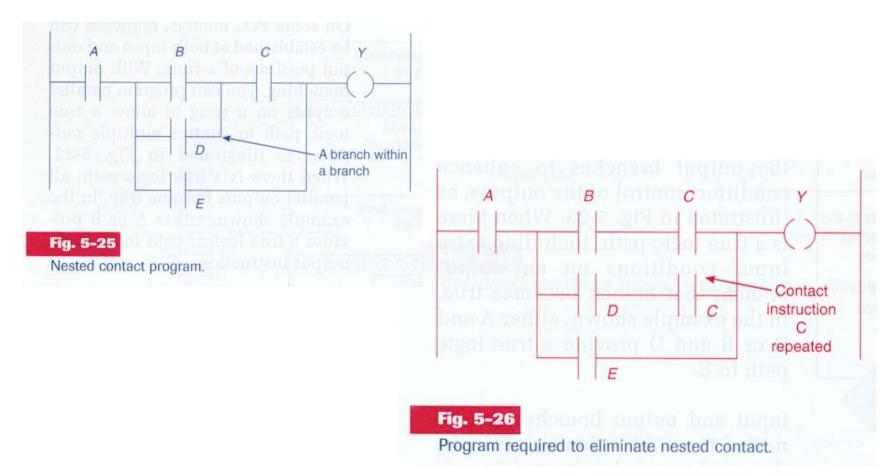

Note: it is important to study the constraints and potentialities of the development tools.

Imbricated contacts and alternative solution

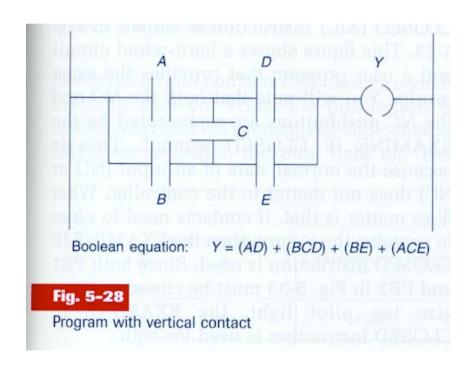

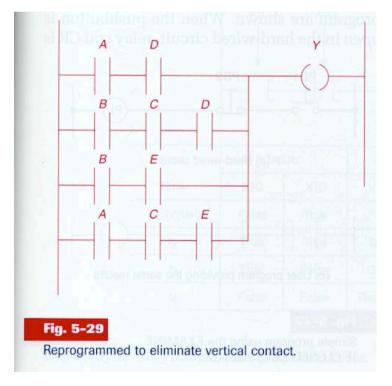

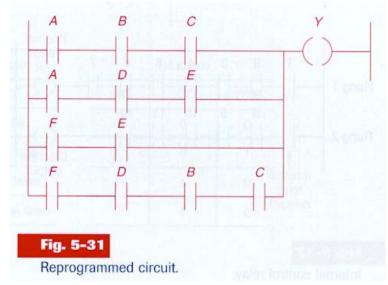

Contacts in the vertical and alternative solution

Contacts in the vertical and alternative solution

### Another example:

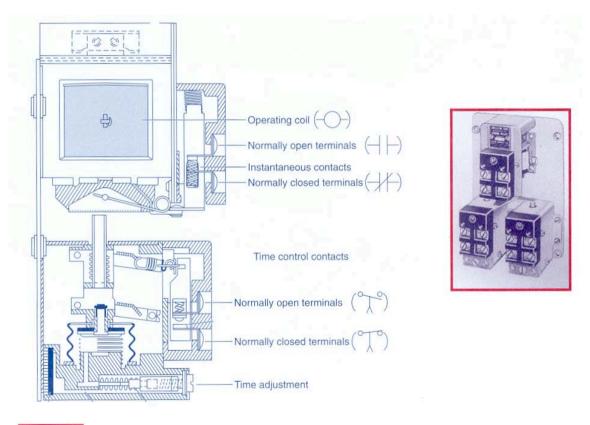

# Temporized Relays

or

### **Timers**

Fig. 7-1

Pneumatic on-delay timer. (Courtesy of Allen-Bradley Company, Inc.)

## Temporized Relays

or

#### **Timers**

### Characteristics:

Identifier:%TMi 0..63 in the TSX37

Input: IN to activate

Mode: TON On delay

TOFF Off delay

TP Monostable

Time basis: TB 1mn (def.), 1s,

100ms, 10ms

Programmed value: %TMi.P 0...9999 (def.)

period=TB\*TMi.P

Actual value: %TMi.V 0...TMi.P

(can be real or tested)

Modifiable: Y/N can be modified from

the console

### Temporized Relays

or

#### **Timers**

### **Example:**

### **Example:**

## Temporized Relays

Mode:

TP

or

Works as a monstable or as a pulse generator (with pre-programmed period)

### **Timers**

Timer address

XXX

# Ladder diagram

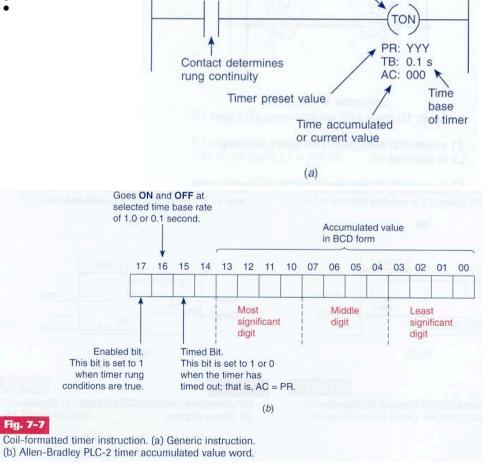

# **Timers** implementation in the Allen-Bradley PLC-5:

#### Two alternative representations....

Type of timer

API P. Oliveira Page 31

Fig. 7-7

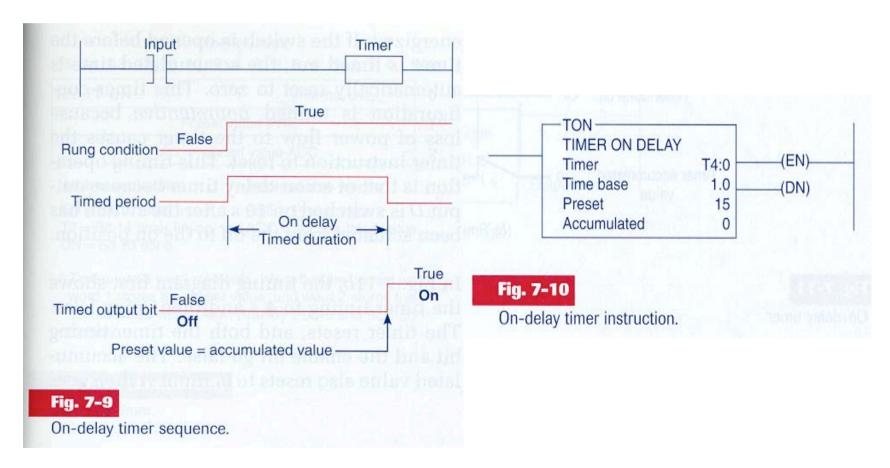

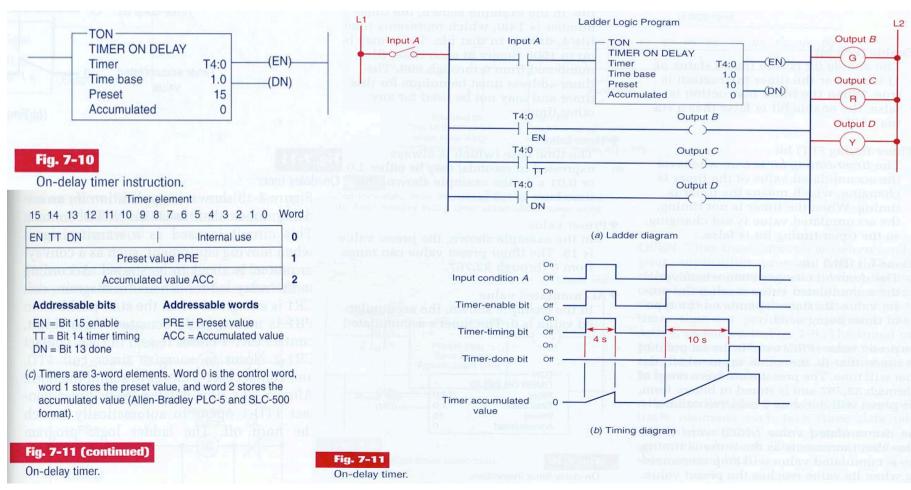

### Timers operation in the Allen-Bradley PLC-5

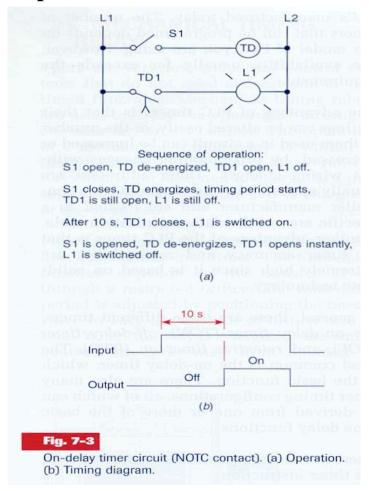

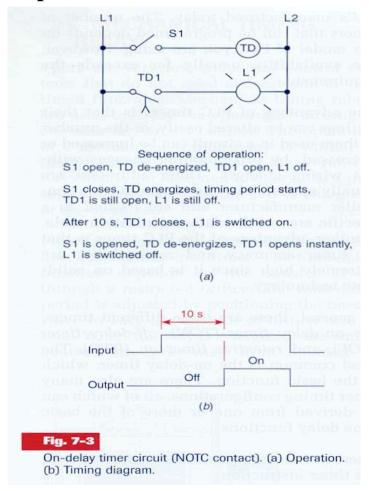

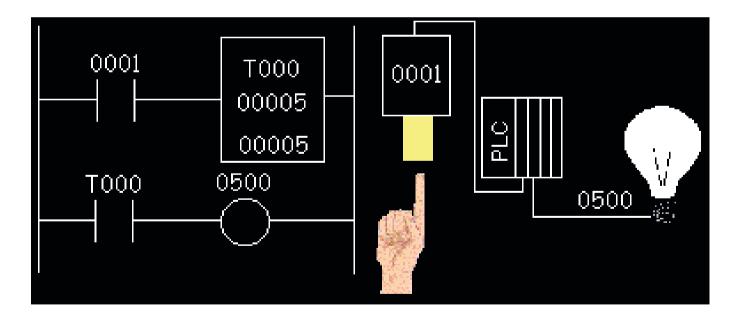

### Example of timer on-delay

API

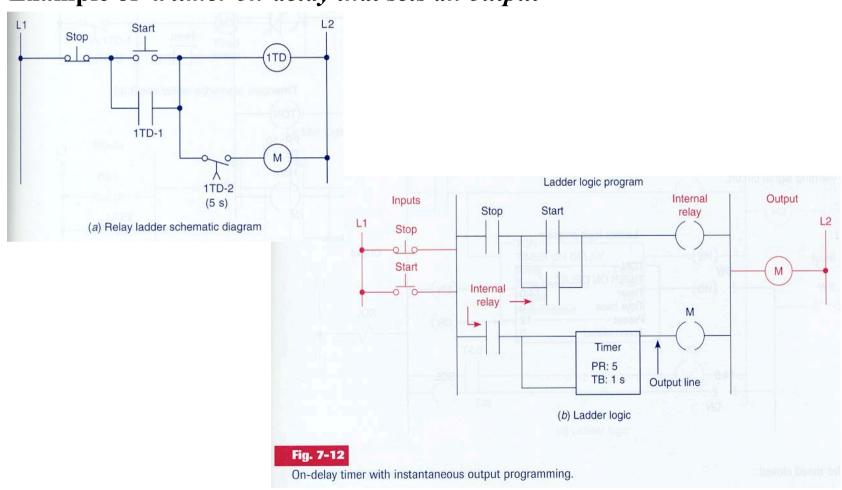

### Example of a timer on-delay that sets an output

## Example of timer on-delay

## Example of timer on-delay

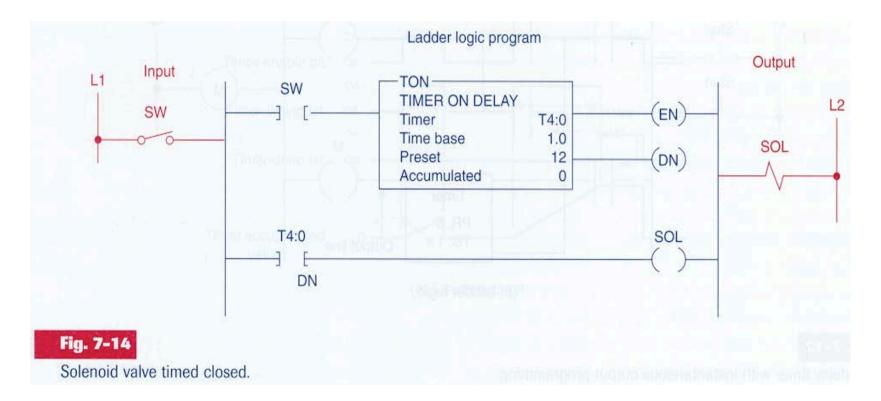

Coil is energized if the switch remains closed for 12 seconds

PS<sub>1</sub>

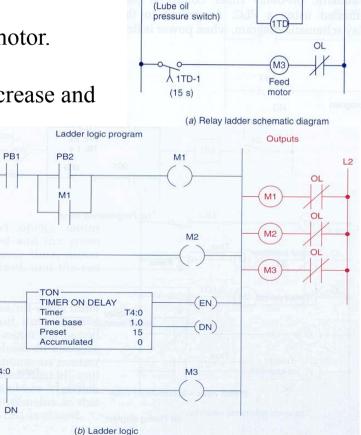

Lube oil pump motor

Main drive motor

## Ladder diagram

## Example of timer on-delay

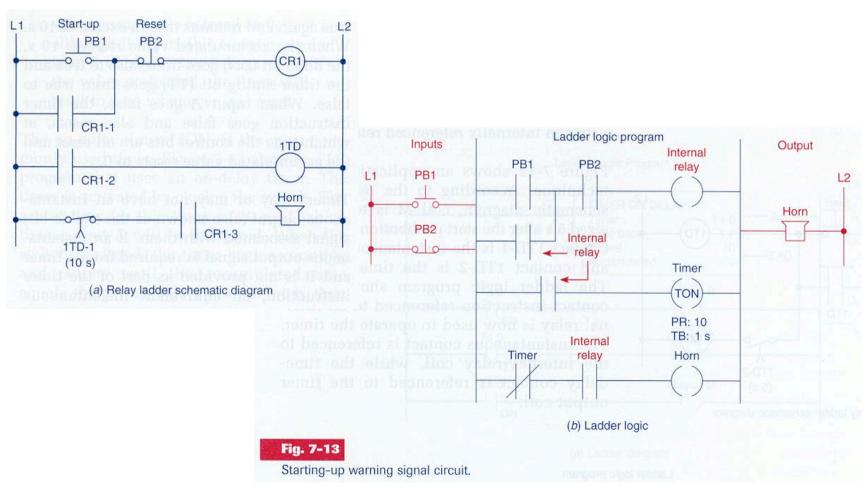

• If PB2 is activated, powers on the oil pumping motor.

• When the pressure augments, PS1 detects the increase and

activates the main motor.

• 15 segunds later the main drive motor starts.

API P. Oliveira Page 37

Automatic sequential control system.

Inputs

PB1

PS1

PB2

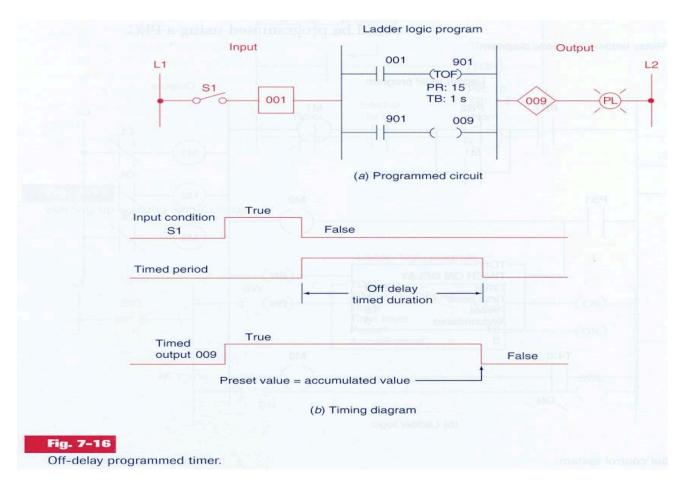

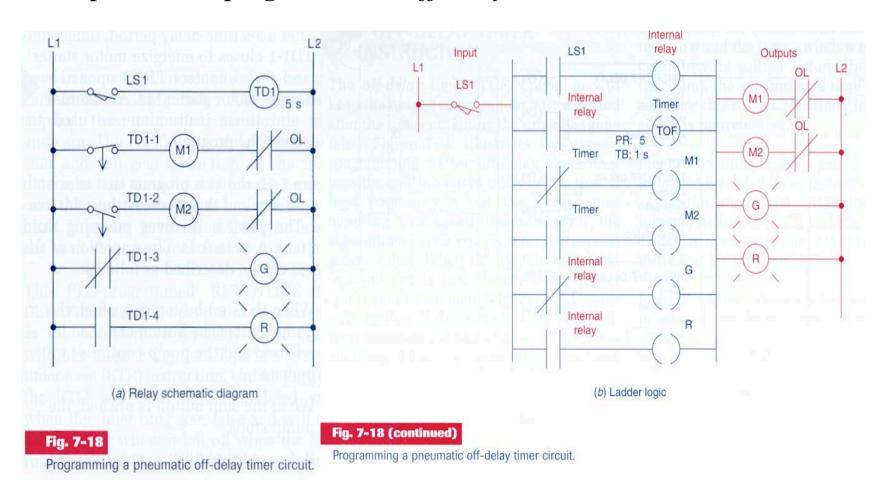

## Example of timer programmed as off-delay

## Example of timer programmed as off-delay

## Example of timer programmed as off-delay

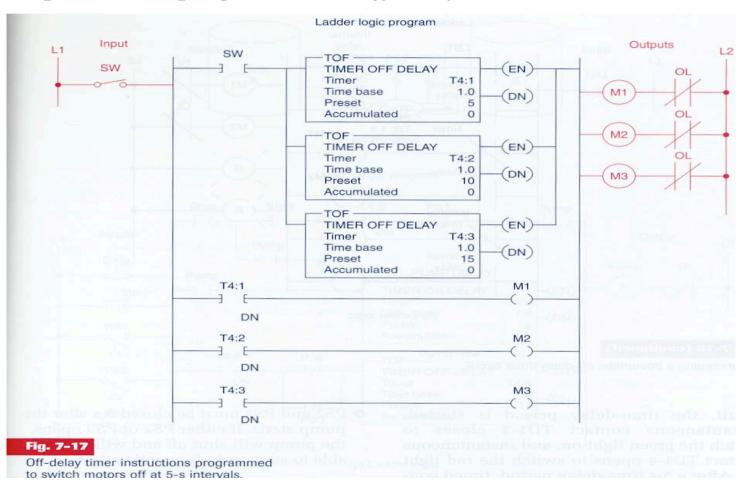

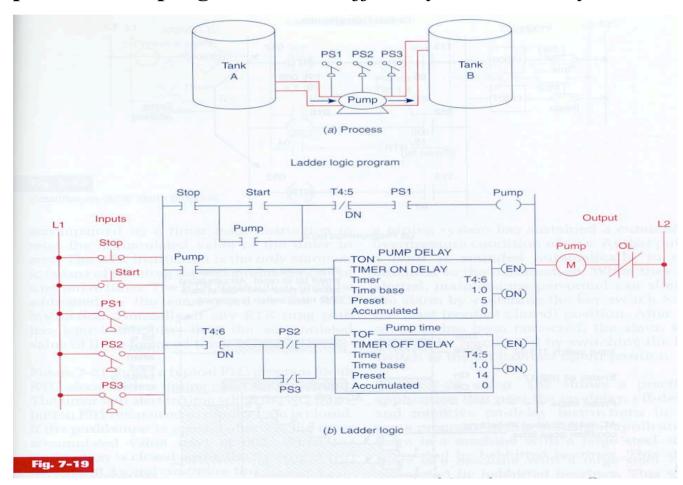

## Example of timers programmed as off-delay and on-delay

## **Timers**

## **Example:**

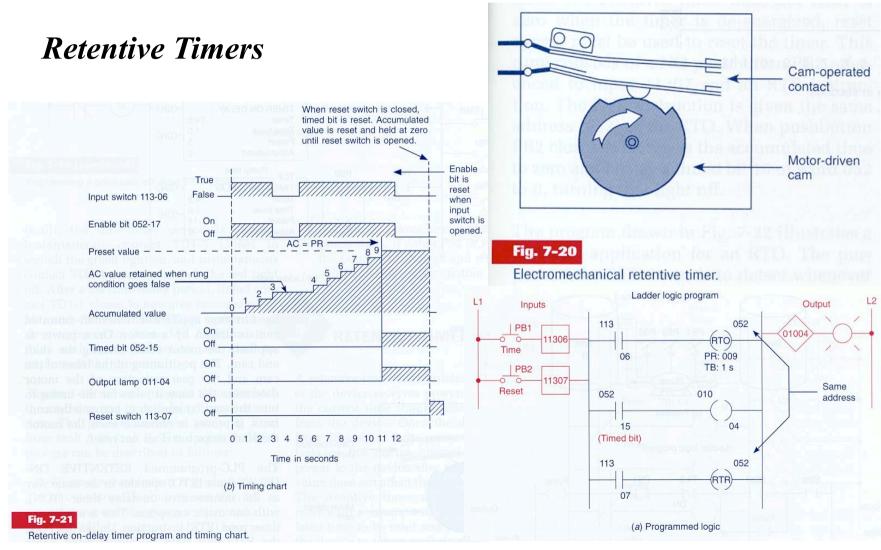

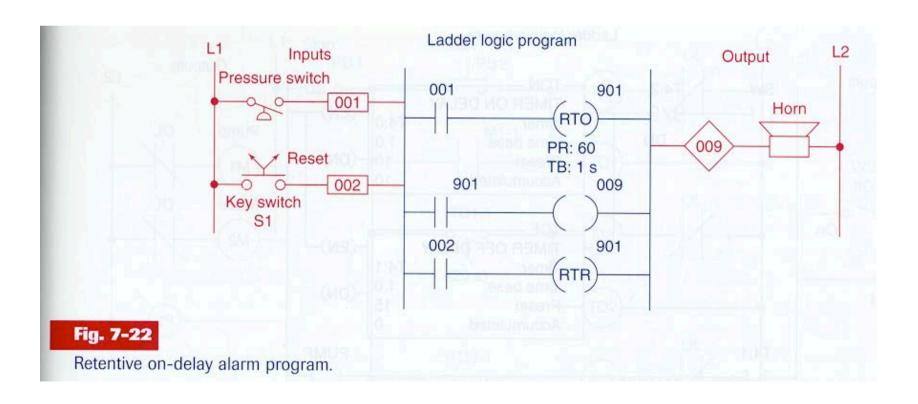

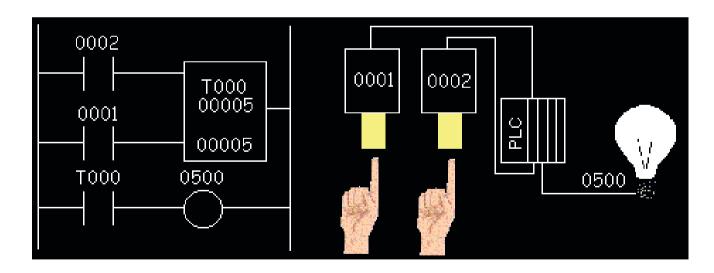

## **Example of** *retentive timers*

## **Timers**

## **Example:**

(search on the Schneider PLC or discuss implementation)

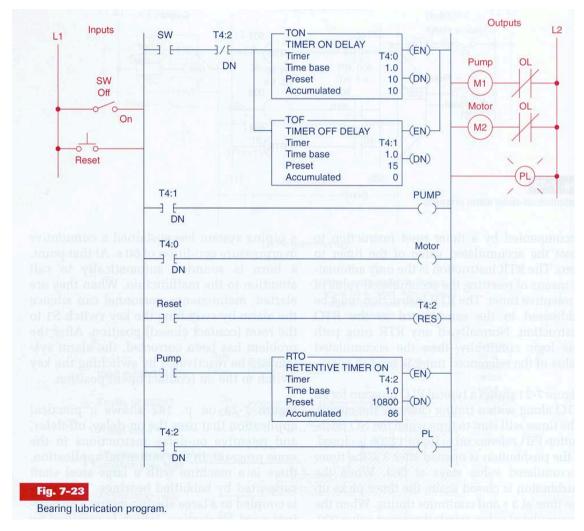

## **Exemplo:**

- SW ON to start operation

- Before motor starts, lubrificate 10 s with oil.

- SW OFF to stop. (lubrificate 15 s more).

- After 3 hours of pump operation, stop motor and signal with pilot light.

- Reset available after servicing.

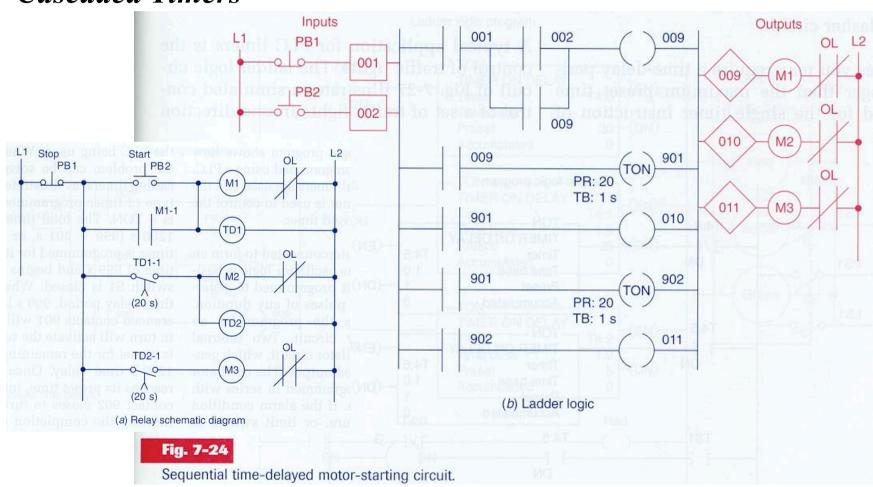

## Cascaded Timers

# Cascaded Timers (bistable system)

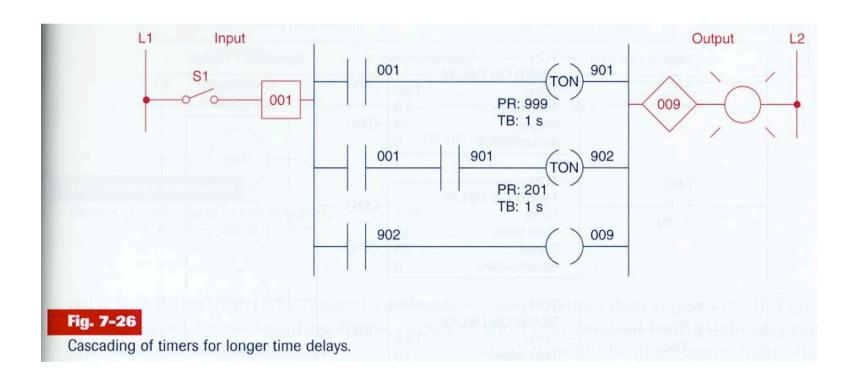

# Timers for very long time intervals

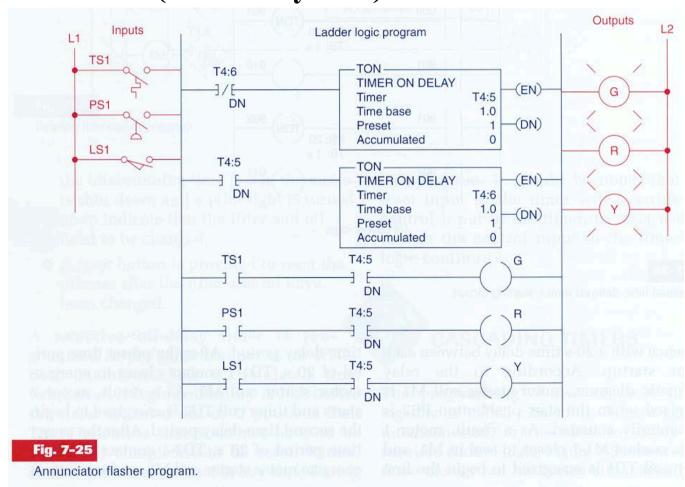

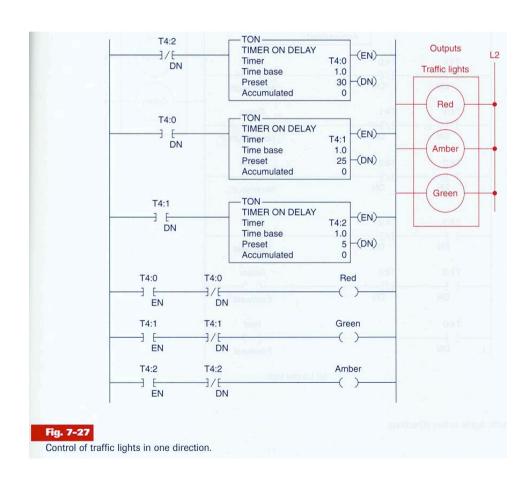

## Example of a semaphore

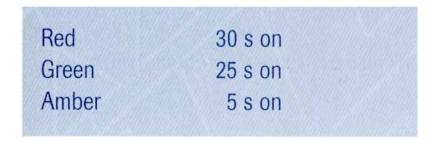

Red 30 s on

Green 25 s on

Amber 5 s on

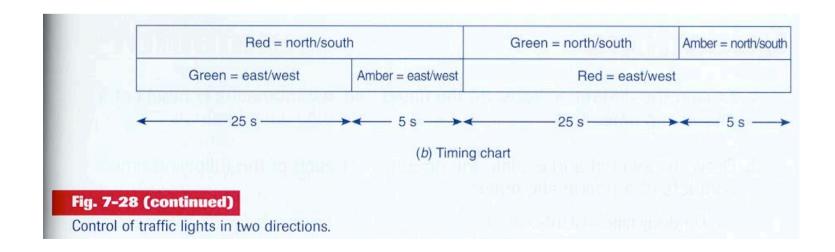

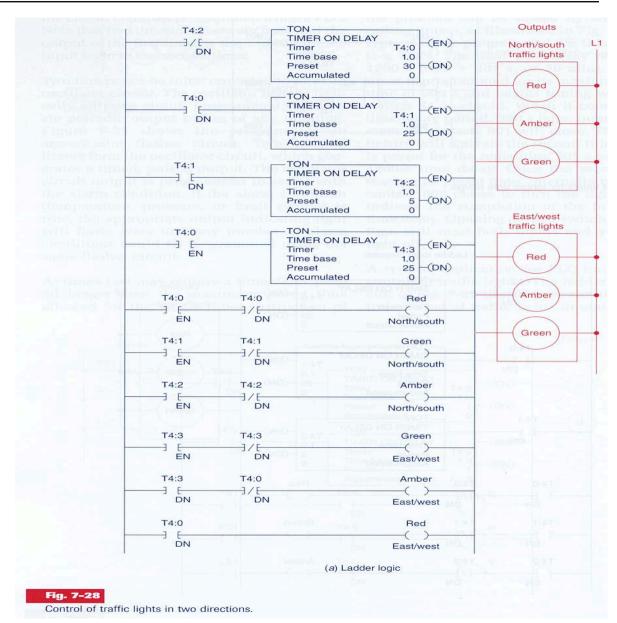

## **Example of a semaphore in both directions**

## **Chap. 3 - PLCs Programming languages**

**Example**

of a

semaphore

in both

directions

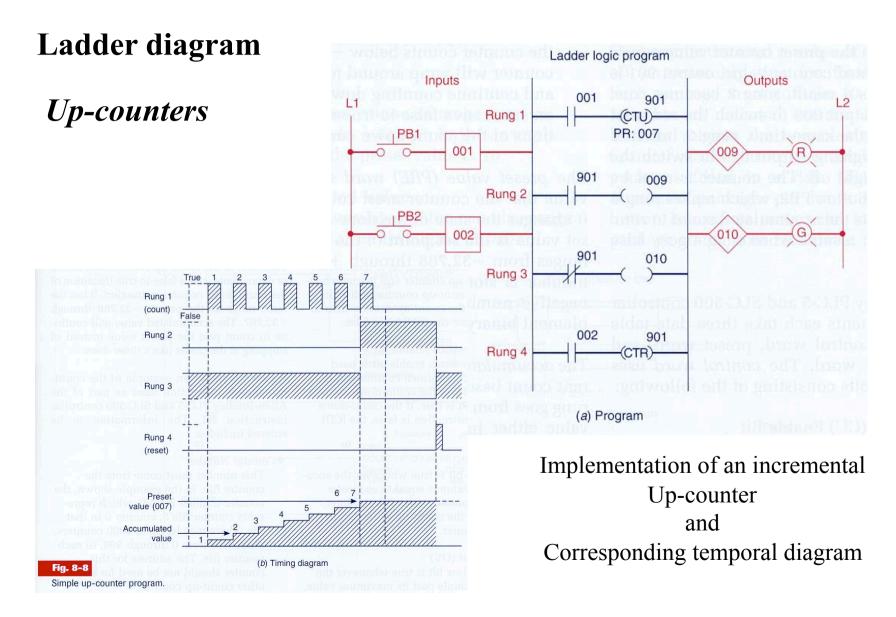

## **Counters**

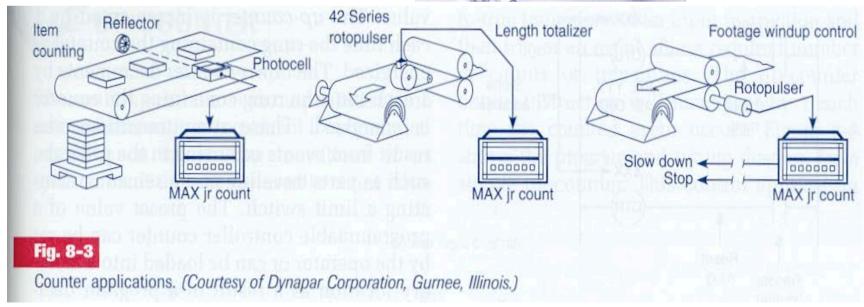

Some applications...

# **Ladder diagram** Characteristics:

## **Counters**

Identifier:%Ci 0...31 in the TSX37

Value progr.: %Ci.P 0...9999 (def.)

Value Actual: 0...Ci.P (only to be read) %Ci.V

Modifiable: Y/N can be modified from

the console

Inputs: Reset Ci.V=0 R

> S Preset Ci.V=Ci.P

CU Count Up

CD Count Down

Overrun %Ci.E=1 %Ci.V=0->9999 Outputs: E

> D Done %Ci.D=1 %Ci.V=Ci.P

F Full %Ci.F=1 %Ci.V=9999->0

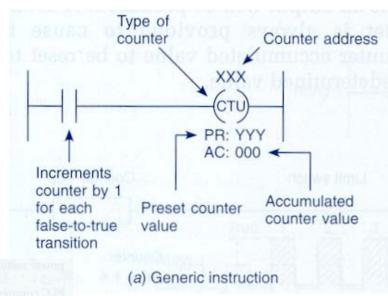

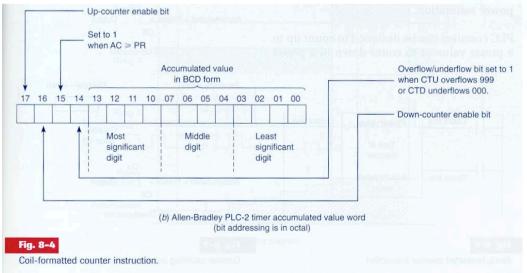

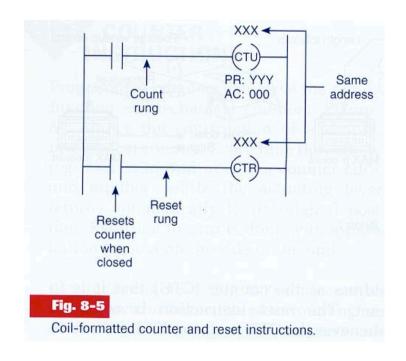

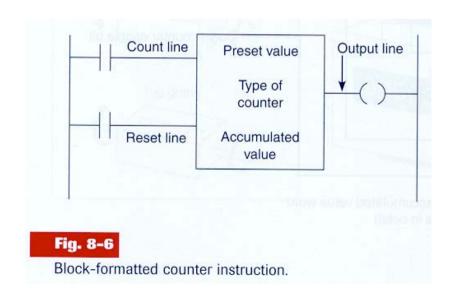

# Implementation of Counters in the PLC-5 of *Allen-Bradley*:

### **Internal Structure**

Representation

# Implementation of Counters in the PLC-5 of *Allen-Bradley*:

### Alternative representations

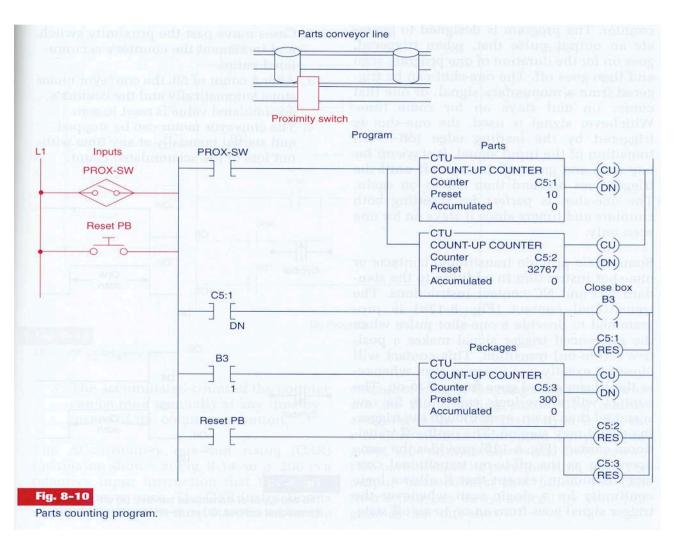

# **Example:**

Counting parts

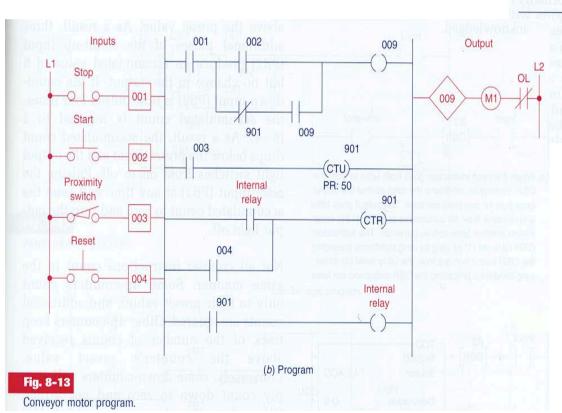

# **Example**

Case

Conveyor motor

Start/stop station

Count reset button

(a) Process flow diagram

Proximity

switch

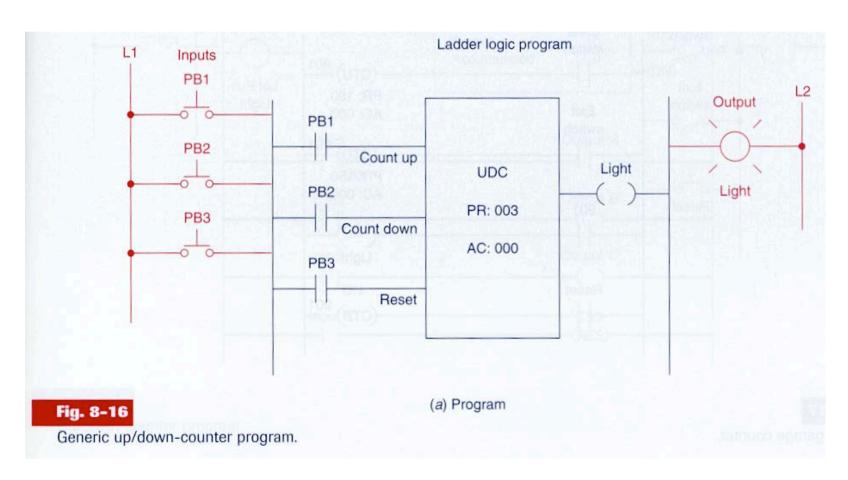

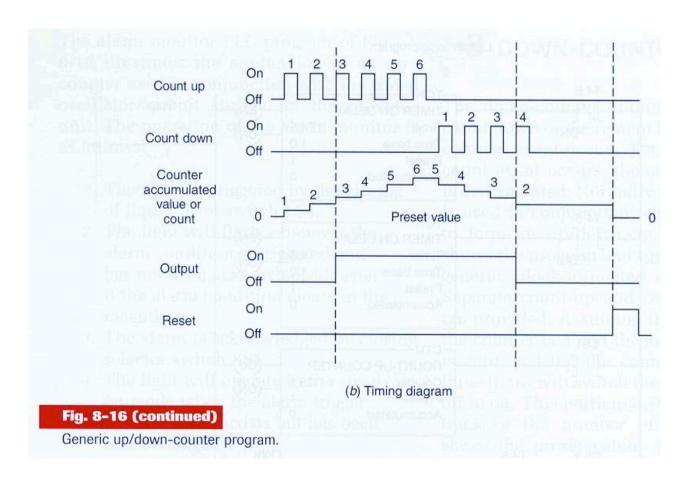

# *Up/down-counters*

# Up/down-counters

# *Up/down-counters*

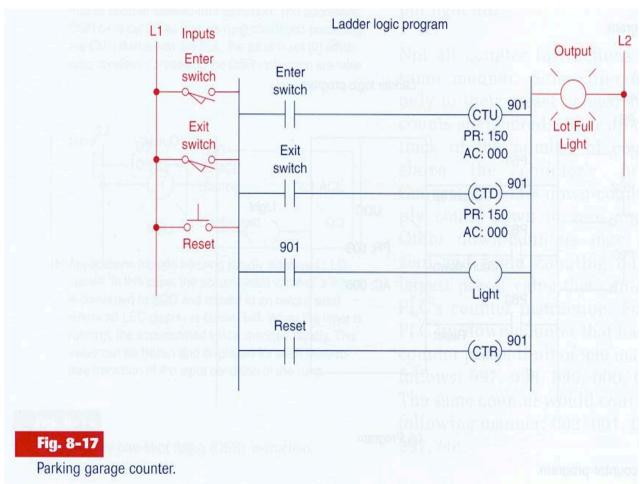

## **Example:**

Finite

parking

garage

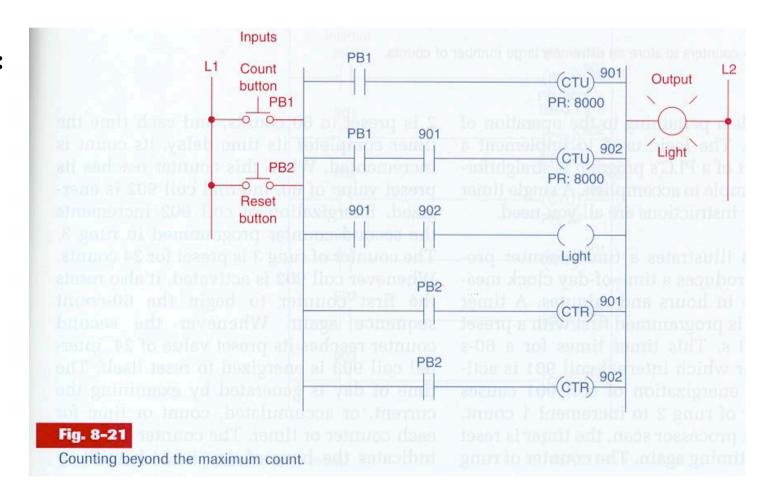

## **Cascaded Counters**

## **Example:**

## **Cascaded Counters**

## **Example:**

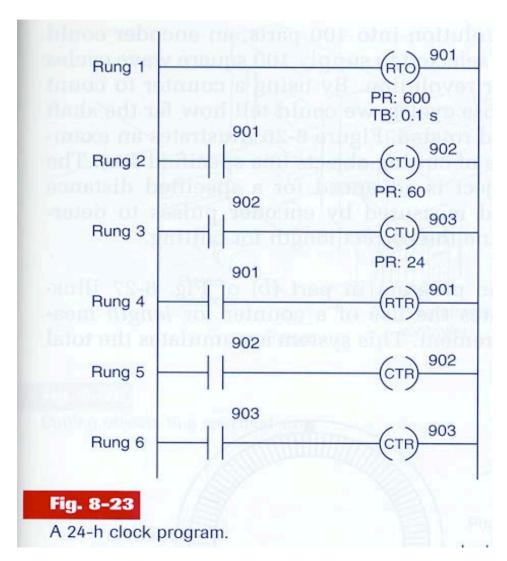

24 hours clock

## **Cascaded Counters**

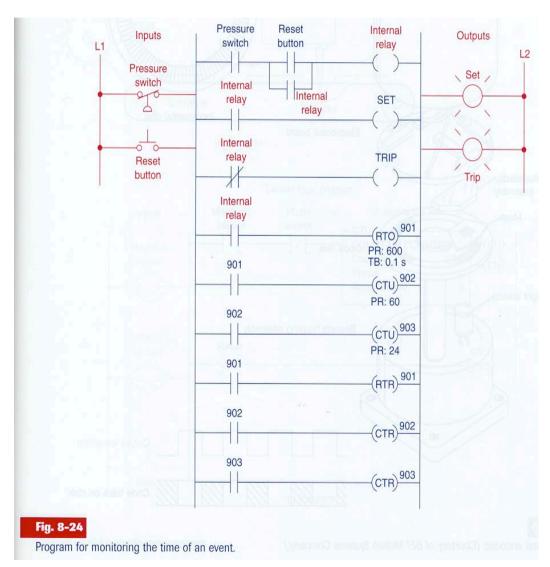

## **Example:**

Memory time of event

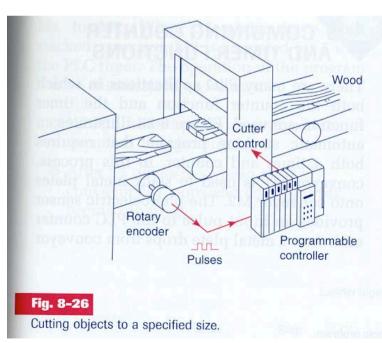

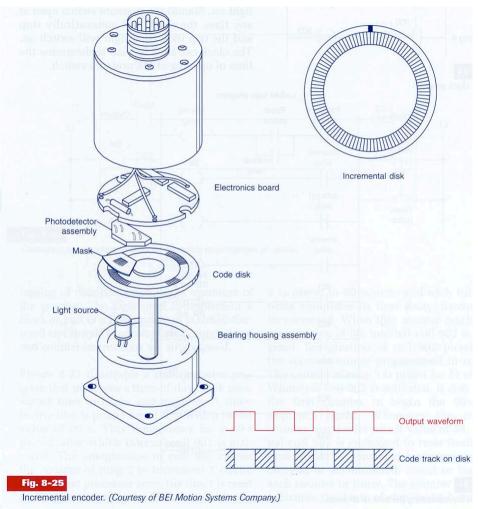

## Incremental Encoder

## **Incremental** Encoder

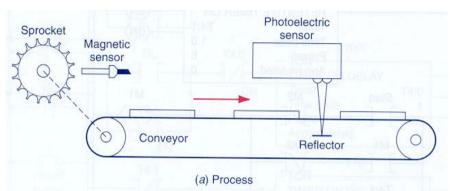

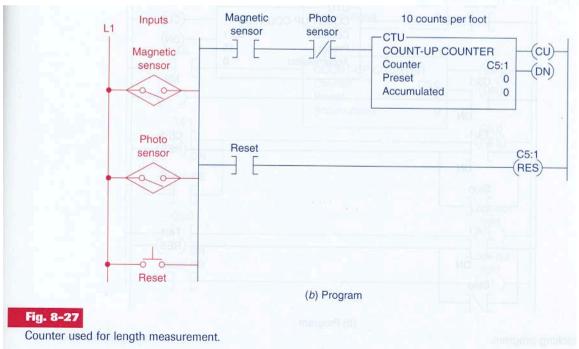

## **Example:**

counter as a "lenght sensor"

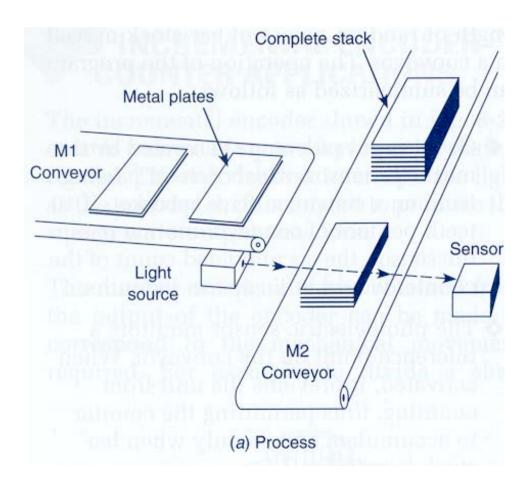

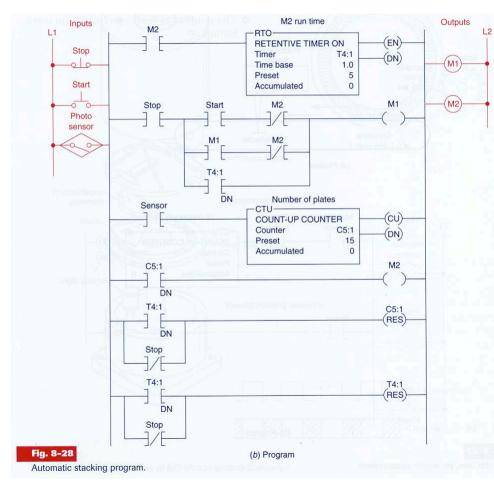

## **Example with counters and timers (conts.):**

## Specs:

- Starts M1 conveyor upon pushing button .

- After 15 plates stops M1 and starts conveyor M2.

- M2 operates for 5 seconds and then stops.

- Restart sequence.

## **Example with counters and timers (conts.):**

## Specs:

- Starts M1 conveyor upon pushing button .

- After 15 plates stops M1 and starts conveyor M2.

- M2 operates for 5 seconds and then stops.

- Restart sequence.

## **Example with counters and timers (conts.):**

## Specs:

- Starts M1 conveyor upon pushing button .

- After 15 plates stops M1 and starts conveyor M2.

- M2 operates for 5 seconds and then stops.

- Restart sequence.

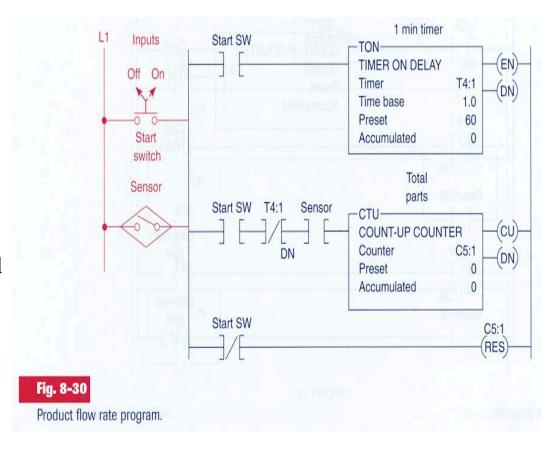

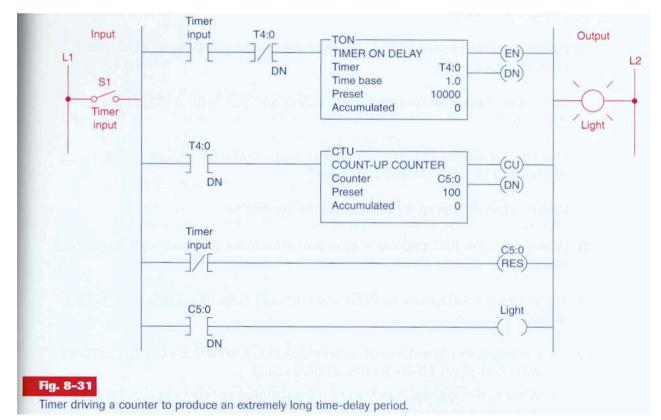

#### **Example with counters and timers (conts.):**

To use a timer to command a counter, to implement large periods of time.

### **Counters**

### **Example:**

### **Numerical Processing**

### **Algebraic and Logic Functions**

```

%Q2.2

%MW50>10

%I1.0

%MW10:=%KW0:=%KW0+10

%I1.2

N INC%MW100

```

### **Numerical Processing**

#### **Arithmetic Functions**

| +   | addition of two operands                  | SQRT | square root of an operand    |

|-----|-------------------------------------------|------|------------------------------|

| -   | subtraction of two operands               | INC  | incrementation of an operand |

| *   | multiplication of two operands            | DEC  | decrementation of an operand |

| 1   | division of two operands                  | ABS  | absolute value of an operand |

| REM | remainder from the division of 2 operands |      |                              |

#### Operands

| Туре                       | Operand 1 (Op1)  | Operand 2 (Op2)                              |

|----------------------------|------------------|----------------------------------------------|

| Indexable words            | %MW              | %MW,%KW,%Xi.T                                |

| Non-indexable words        | %QW,%SW,%NW,%BLK | Imm.Val.,%IW,%QW,%SW,%NW,<br>%BLK, Num.expr. |

| Indexable double words     | %MD              | %MD,%KD                                      |

| Non-indexable double words | %QD,%SD          | Imm.Val.,%ID,%QD,%SD, Numeric expr.          |

#### **Numerical Processing**

#### **Example:**

Use of a system variable:

%S18 – flag de overflow P. Oliveira

### **Numerical Processing**

#### **Logic Functions**

| AND | AND (bit by bit) between two operands          |

|-----|------------------------------------------------|

| OR  | logical OR (bit by bit) between two operands   |

| XOR | exclusive OR (bit by bit) between two operands |

| NOT | logical complement (bit by bit) of an operand  |

Comparison instructions are used to compare two operands.

- >: tests whether operand 1 is greater than operand 2,

- >=: tests whether operand 1 is greater than or equal to operand 2,

- <: tests whether operand 1 is less than operand 2,</li>

- <=: tests whether operand 1 is less than or equal to operand 2,

- =: tests whether operand 1 is different from operand 2.

#### Operands

| Туре                       | Operands 1 and 2 (Op1 and Op2)               |

|----------------------------|----------------------------------------------|

| Indexable words            | %MW,%KW,%Xi.T                                |

| Non-indexable words        | Imm.val.,%IW,%QW,%SW,%NW,%BLK, Numeric Expr. |

| Indexable double words     | %MD,%KD                                      |

| Non-indexable double words | Imm.val.,%ID,%QD,%SD,Numeric expr.           |

#### **Numerical Processing**

### **Example:**

Logic functions

### **Numerical Processing**

### Priorities on the execution of the operations

| Rank | Instruction               |

|------|---------------------------|

| 1    | Instruction to an operand |

| 2    | *,/,REM                   |

| 3    | +,-                       |

| 4    | <,>,<=,>=                 |

| 5    | =,<>                      |

| 6    | AND                       |

| 7    | XOR                       |

| 8    | OR                        |

**Structures for Control of Flux**

**Subroutines**

Call and Return

#### **Structures for Control of Flux**

#### **JUMP instructions:**

#### Conditional and unconditional

Jump instructions are used to go to a programming line with an %Li label address:

- JMP: unconditional program jump

- JMPC: program jump if the instruction's Boolean result from the previous test is set at 1

- JMPCN: program jump if the instruction's Boolean result from the previous test is set at 0. %Li is the label of the line to which the jump has been made (address i from 1 to 999 with maximum 256 labels)

#### **Structures for Control of Flux**

#### **Example:**

Use of jump instructions

#### **Attention to:**

- INFINITE LOOPS ...

- It is not a good style of programming!...

- Does not improove the legibility of the proposed solution.

#### **Structures for Control of Flux**

#### Halt

Stops all processes!

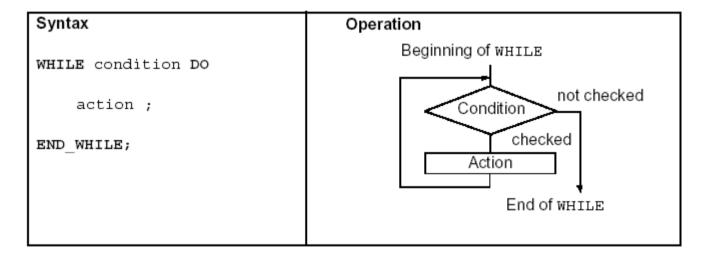

#### **Events masking**

There are other advanced instrauctions (see manuel)

- Monostable

- Registers of 256 words (LIFO ou FIFO)

- DRUMs

- Comparators

- Shift-registers

•••

- Functions to manipulate *floats*

- Functions to convert bases and types

#### **Numerical Tables**

| Туре           | Format         | Maximum<br>address | Size            | Write access |

|----------------|----------------|--------------------|-----------------|--------------|

| Internal words | Simple length  | %MWi:L             | i+L<=Nmax (1)   | Yes          |

|                | Double length  | %MWDi:L            | i+L<=Nmax-1 (1) | Yes          |

|                | Floating point | %MFi:L             | i+L<=Nmax-1 (1) | Yes          |

| Constant words | Single length  | %KWi:L             | i+L<=Nmax (1)   | No           |

|                | Double length  | %KWDi:L            | i+L<=Nmax-1 (1) | No           |

|                | Floating point | %KFi:L             | i+L<=Nmax-1 (1) | No           |

| System word    | Single length  | %SW50:4 (2)        | -               | Yes          |

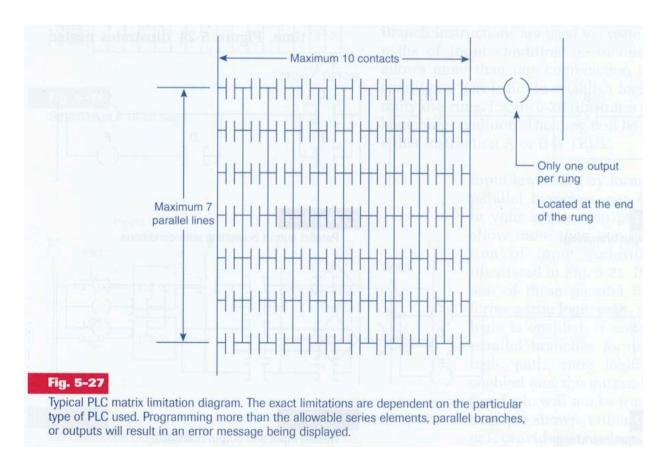

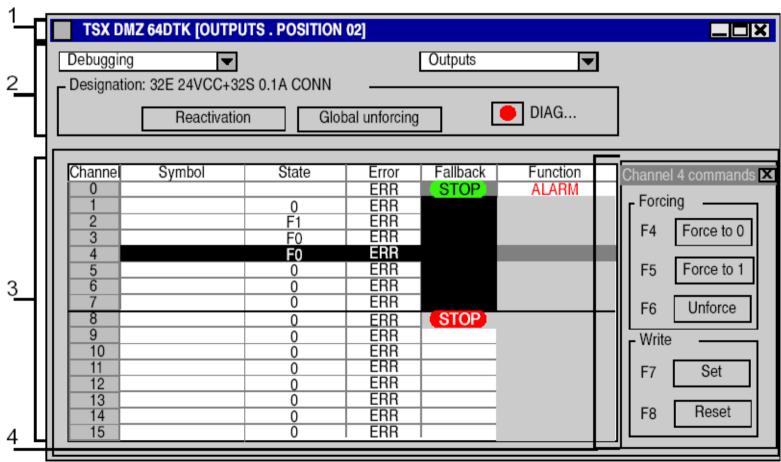

Each PLC has limitations in terms of connections

#### **Example:**

It is important to learn the potentialities and ...

the limitations of the developing tools,

i.e. "TO STUDY the manuals is a MUST."

Learn how to develop and debug programs (and how to do the fine tunning).

**System information: system bits**

| Bit | Function            | Description                                                                                                                                                                                                                                                                             | Initial<br>state | TSX37 | TSX57 |

|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-------|

| %S0 | Cold start          | Normally on 0, this bit is set on 1 by:  loss of data on power restart (battery fault), the user program, the terminal, cartridge uploading, pressing on the RESET button. This bit goes to 1 during the first complete cycle. It is reset to 0 before the following cycle. (Operation) | 0                | YES   | YES   |

| %S1 | Warm restart        | Normally on 0, this bit is set on 1 by:  power restart with data save,  the user program,  the terminal.  It is reset to 0 by the system at the end of the first complete cycle and before output is updated.  (Operation)                                                              | 0                | YES   | YES   |

| %S4 | Time base<br>10ms   | An internal timer regulates the change in status of this bit. It is asynchronous in relation to the PLC cycle.  Graph:    5ms   5ms   5ms                                                                                                                                               | -                | YES   | YES   |

| %S5 | Time base 100<br>ms | Idem %S4                                                                                                                                                                                                                                                                                | -                | YES   | YES   |

| %S6 | Time base 1 s       | Idem %S4                                                                                                                                                                                                                                                                                | -                | YES   | YES   |

| %S7 | Time base 1<br>mn   | Idem %S4                                                                                                                                                                                                                                                                                | -                | YES   | YES   |

See manual for the remaining 100 bits generated...

#### Informação de Sistema: words de sistema

| Words | Function                             | Description                                                                                                                                                                                                                                                                                                   | Management |

|-------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| %SW0  | Master task<br>scanning period       | The user program or the terminal modify the duration of the master task defined in configuration. The duration is expressed in ms (1.255 ms) %SW0=0 in cyclic operation. On a cold restart: it takes on the value defined by the configuration.                                                               | User       |

| %SW1  | Fast task scanning period            | The user program or the terminal modify the duration of the fast task as defined in configuration.  The duration is expressed in ms (1.255 ms)  On a cold restart: it takes on the value defined by the configuration.                                                                                        |            |

| %SW8  | Acquisition of task input monitoring | Normally on 0, this bit can be set on 1 or 0 by the program or the terminal.  It inhibits the input acquisition phase of each task.  SSW8:X0 =1 assigned to MAST task: outputs linked to this task are no longer guided.  SSW8:X1 =1 assigned to FAST task: outputs linked to this task are no longer guided. | User       |

| %SW9  | Monitoring of task output update     | Normally on 0, this bit can be set on 1 or 0 by the program or the terminal.  Inhibits the output updating phase of each task.  ◆ %SW9:X0 =1 assigned to MAST task: outputs linked to this task are no longer guided.  ◆ %SW9:X1 =1 assigned to FAST task: outputs linked to this task are no longer guided.  | User       |

| %SW10 | First cycle after cold start         | If the bit for the current task is on 0, this indicates that the first cycle is being carried out after a cold start.  • %SW10:X0: is assigned to the MAST Master task  • %SW10:X1: is assigned to the FAST fast task                                                                                         | System     |

| %SW11 | Watchdog duration                    | Reads the duration of the watchdog as set in configuration. It is expressed in ms (10500 ms).                                                                                                                                                                                                                 | System     |

See manual for the remaining 140 words generated...

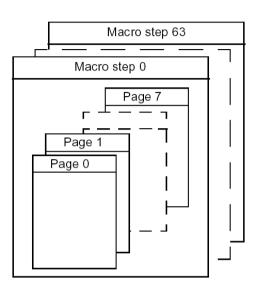

**Software Organization**

**MAST** – Master Task Program

**Composed by sections**

**Execution**

**Cyclically**

or

Periodically

Sas (LD)

Oven1 (GRAFCET)

PRL (LD)

Chart

POST (IL)

Drying (LD)

Cleaning (IL)

**Software Organization**

**FAST** – Fast Task Program

**Priority greater than MAST**

- Executed Periodically (1-255ms)

- Verified by a Watchdog, impacts on %S11

- %S31 Enables or disables a FAST

- %S33 gives the execution time for FAST

**Software Organization**

**Event Processes** – Processes that can react to external changes (16 in the Micro 3722 EV0 a EV15)

**Priority greater than MAST and FAST!**

## **Event Generators**

- Inputs 0 to 3 in module 1, given transictions

- Counters

- Upon telegrams reception

- %S38 Enables or disables event processes

(also with MASKEVT() or UNMASKEVT())

# **Industrial Automation**

(Automação de Processos Industriais)

# PLCs Programming Languages Structured Text

http://www.isr.ist.utl.pt/~pjcro/courses/api1011/api1011.html

Prof. Paulo Jorge Oliveira pjcro @ isr.ist.utl.pt Tel: 21 8418053 ou 2053 (internal)

# Syllabus:

Chap. 2 – Introduction to PLCs [2 weeks]

•••

Chap. 3 – PLCs Programming Languages [2 weeks]

Standard languages (IEC-1131-3):

Ladder Diagram; Instruction List, and Structured Text.

Software development resources.

•••

Chap. 4 - GRAFCET (Sequential Function Chart) [1 week]

# PLCs Programming Languages (IEC 1131-3)

## Ladder Diagram

#### Structured Text

If %I1.0 THEN %Q2.1 := TRUE ELSE %Q2.2 := FALSE END\_IF

#### Instruction List

LD %M12 AND %I1.0 ANDN %I1.1 OR %M10 ST %Q2.0

# Sequential Function Chart (GRAFCET)

# Linguagens de programação de PLCs (IEC 1131-3)

## Ladder Diagram

#### Structured Text

If %I1.0 THEN

%Q2.1 := TRUE

ELSE

%Q2.2 := FALSE

END\_IF

#### Instruction List

LD %M12 AND %I1.0 ANDN %I1.1 OR %M10 ST %Q2.0

# Sequential Function Chart (GRAFCET)

```

(* Searching for the first element that is not zero

in a

table of 32 words, determining its value

(%MW10), its rank (%MW11). This search

is done if %MO is set to 1, %M1 is set to 1 if

an element which is not zero exists unless it is

set to 0*)

IF %MO THEN

FOR %MW99:=0 TO 31 DO

IF %MW100[%MW99]<>0 THEN

%MW10:=%MW100[%MW99];

%MW11:=%MW99;

%M1:=TRUE;

EXIT; (*Exit the loop*)

ELSE

%M1:=FALSE;

END IF;

END FOR;

ELSE

%M1:=FALSE;

END IF;

```

## A section of the program is composed by sequences

One sequence is equivalent to a section in *ladder diagram* (one or more rangs).

```

1 _____%L20: (*Awaiting drying*) ______ 2

SET %M0;

%MW4:=%MW2 + %MW9; _____ 3

(*calculating pressure*)

%MF12:=SQRT (%MF14);

```

#### Legend:

- 1 label unique identifier (%Li, i=0...999)

- 2 comments augments legibility (\* limited to 256 bytes \*)

- 3 instructions

#### **Basic Instructions**

#### Load

#### **Basic Instructions**

#### Store

# **Structured Text Basic Instructions**

AND

**AND**

AND(NOT...)

AND(RE...)

AND(FE...)

AND of the operand with the result of the previous logical operation.

AND of the operand with the inverted result of the previous logical operation.

AND of the rising edge with the result of the previous logical operation.

AND of the falling edge with the result of the previous logical operation.

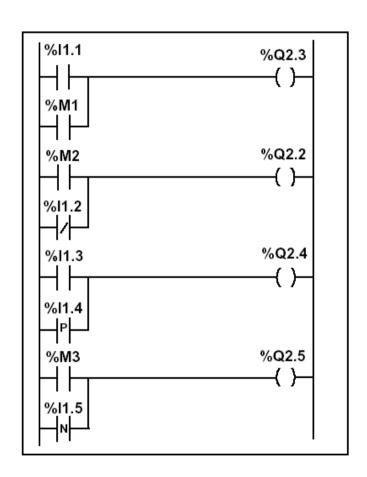

# **Structured Text Basic Instructions**

OR

**OR**

OR(NOT...)

OR(RE...)

OR(FE...)

OR of the operand with the result of the previous logical operation.

OR of the operand with the inverted result of the previous logical operation.

OR of the rising edge with the result of the previous logical operation.

OR of the falling edge with the result of the previous logical operation.

#### **Example:**

```

%Q2.3:=%I1.1 OR %M1;

%Q2.2:=%M2 OR (NOT%I1.2);

%Q2.4:=%I1.3 OR (RE%I1.4);

%Q2.5:=%M3 OR (FE%I1.5);

```

### **Basic Instructions**

#### **XOR**

%Q2.3:=%I1.1 XOR%M1; %Q2.2:=%M2 XOR (NOT%I1.2); %Q2.4:=%I1.3 XOR (RE%I1.4) %Q2.5:=%M3 XOR (FE%I1.5);

| Instruction<br>list | Structured text | Description                                                                                    | Timing diagram                        |

|---------------------|-----------------|------------------------------------------------------------------------------------------------|---------------------------------------|

| XOR                 | XOR             | OR Exclusive between the operand and the previous instruction's Boolean result                 | XOR<br>%I1.1<br>%M1<br>%Q2.3          |

| XORN                | XOR (NOT)       | OR Exclusive between the operand inverse and the previous instruction's Boolean result         | XORN<br>                              |

| XORR                | XOR (RE)        | OR Exclusive between the operand's rising edge and the previous instruction's Boolean result   | XORR<br>  %I1.3<br>  %I1.4<br>  %Q2.4 |

| XORF                | XOR (FE)        | OR Exclusive between the operand's falling edge and the previous instruction's Boolean result. | XORF<br>%M3<br>%I1.5<br>%Q2.5         |

# **Basic Instructions to Manipulate Bit Tables**

| Designation          | Function                                                       |

|----------------------|----------------------------------------------------------------|

| Table:= Table        | Assignment between two tables                                  |

| Table:= Word         | Assignment of a word to a table                                |

| Word:= Table         | Assignment of a table to a word                                |

| Table:= Double word  | Assignment of a double word to a table                         |

| Double word: = Table | Assignment of a table to a double word                         |

| COPY_BIT             | Copy of a bits table in a bits table                           |

| AND_ARX              | AND between two tables                                         |

| OR_ARX               | OR between two tables                                          |

| XOR_ARX              | exclusive OR between two tables                                |

| NOT_ARX              | Negation in a table                                            |

| BIT_W                | Copy of a bits table in a word table                           |

| BIT_D                | Copy of a bits table in a double word table                    |

| W_BIT                | Copy of a word table in a bits table                           |

| D_BIT                | Copy of a double word table in a bits table                    |

| LENGHT_ARX           | Calculation of the length of a table by the number of elements |

## Temporized Relays

or

### **Timers**

Fig. 7-1

Pneumatic on-delay timer. (Courtesy of Allen-Bradley Company, Inc.)

# Temporized Relays

or

#### **Timers**

# Characteristics:

Identifier:%TMi 0..63 in the TSX37

Input: IN to activate

Mode: TON On delay

TOFF Off delay

TP Monostable

Time basis: TB 1mn (def.), 1s,

100ms, 10ms

Programmed value: %TMi.P 0...9999 (def.)

period=TB\*TMi.P

Actual value: %TMi.V 0...TMi.P

(can be real or tested)

Modifiable: Y/N can be modified from

the console

# Relés temporizados Ou Timers

# **Example:**

# **Counters**

Some applications...

# **Counters**

# Characteristics:

Identifier:%Ci 0..31 in the TSX37

Value progr.: %Ci.P 0...9999 (def.)

Value Actual: %Ci.V 0...Ci.P (only to be read)

Modifiable: Y/N can be modified from

the console

Inputs: R Reset Ci.V=0

S Preset Ci.V=Ci.P

CU Count Up

CD Count Down

Outputs: E Overrun %Ci.E=1 %Ci.V=0->9999

D Done %Ci.D=1 %Ci.V=Ci.P

F Full %Ci.F=1 %Ci.V=9999->0

# **Counters**

**Example:**

IF %I1.1 THEN

RESET %C8;

END\_IF;

IF (%I1.2 AND %M0) THEN

UP %C8;

END\_IF; %Q2.0 := %C8.D;

#### Instruction list language

LD %I1.1

R %C8

LD %I1.2

AND %M0

CU %C8

LD %C8.D

ST %Q2.0

# **Numerical Processing**

# **Algebraic and Logic Functions**

```

%Q2.2:=%MW50 > 10;

IF %I1.0 THEN

%MW10:=%KW0 + 10;

END_IF;

IF FE %I1.2 THEN

INC %MW100;

END_IF;

```

# **Numerical Processing**

#### **Arithmetic Functions for Words**

| +   | addition of two operands                                  | SQRT | square root of an operand    |

|-----|-----------------------------------------------------------|------|------------------------------|

| -   | subtraction of two operands                               | INC  | incrementation of an operand |

| *   | multiplication of two operands                            | DEC  | decrementation of an operand |

| 1   | division of two operands ABS absolute value of an operand |      | absolute value of an operand |

| REM | remainder from the division of 2 operands                 |      |                              |

#### Operands

| Туре                       | Operand 1 (Op1)  | Operand 2 (Op2)                              |

|----------------------------|------------------|----------------------------------------------|

| Indexable words            | %MW              | %MW,%KW,%Xi.T                                |

| Non-indexable words        | %QW,%SW,%NW,%BLK | Imm.Val.,%IW,%QW,%SW,%NW,<br>%BLK, Num.expr. |

| Indexable double words     | %MD              | %MD,%KD                                      |

| Non-indexable double words | %QD,%SD          | Imm.Val.,%ID,%QD,%SD, Numeric expr.          |

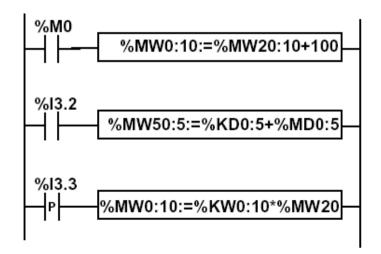

# **Numerical Processing**

# **Example:**

#### Arithmetic functions

#### Instruction list language

```

LD %M0

[%MW0:=%MW10+100]

LD %I3.2

[%MW0:=SQRT(%MW10)]

LD %I3.3

[INC %MW100]

```

# **Numerical Processing**

# **Example:**

Arithmetic functions

#### Example in instruction list language:

```

LD %M0

[%MW0:=%MW1+%MW2]

LDN %S18

[%MW10:=%MW0]

LD %S18

[%MW10:=32767]

R %S18]

```

# **Numerical Processing**

# **Logic Functions**

| AND (bit by bit) between two operands              |                                               |

|----------------------------------------------------|-----------------------------------------------|

| OR                                                 | logical OR (bit by bit) between two operands  |

| XOR exclusive OR (bit by bit) between two operands |                                               |

| NOT                                                | logical complement (bit by bit) of an operand |

Comparison instructions are used to compare two operands.

- >: tests whether operand 1 is greater than operand 2,

- >=: tests whether operand 1 is greater than or equal to operand 2,

- <: tests whether operand 1 is less than operand 2,</li>

- <=: tests whether operand 1 is less than or equal to operand 2,

- =: tests whether operand 1 is different from operand 2.

#### Operands

| Туре                       | Operands 1 and 2 (Op1 and Op2)               |

|----------------------------|----------------------------------------------|

| Indexable words            | %MW,%KW,%Xi.T                                |

| Non-indexable words        | Imm.val.,%IW,%QW,%SW,%NW,%BLK, Numeric Expr. |

| Indexable double words     | %MD,%KD                                      |

| Non-indexable double words | Imm.val.,%ID,%QD,%SD,Numeric expr.           |

# **Numerical Processing**

# **Example:**

Logic functions

# Structured text language

```

%Q2.3:=%MW10>100;

%Q2.2:=%M0 AND (%MW20<%KW35);

%Q2.4:=%I1.2 OR (%MW30>=%MW40);

```

# **Numerical Processing**

# **Example:**

Numeric Tables Manipulation

# **Numerical Processing**

# Priorities on the execution of the operations

| Rank | Instruction               |

|------|---------------------------|

| 1    | Instruction to an operand |

| 2    | *,/,REM                   |

| 3    | +,-                       |

| 4    | <,>,<=,>=                 |

| 5    | =,<>                      |

| 6    | AND                       |

| 7    | XOR                       |

| 8    | OR                        |

#### **Structures for Control of Flux**

#### **Subroutines**

Call and Return

# Structured text language

# Structured text language

#### **Structures for Control of Flux**

#### **JUMP instructions:**

#### Conditional and unconditional

Jump instructions are used to go to a programming line with an %Li label address:

- JMP: unconditional program jump

- JMPC: program jump if the instruction's Boolean result from the previous test is set at 1

- JMPCN: program jump if the instruction's Boolean result from the previous test is set at 0. %Li is the label of the line to which the jump has been made (address i from 1 to 999 with maximum 256 labels)

#### **Structures for Control of Flux**

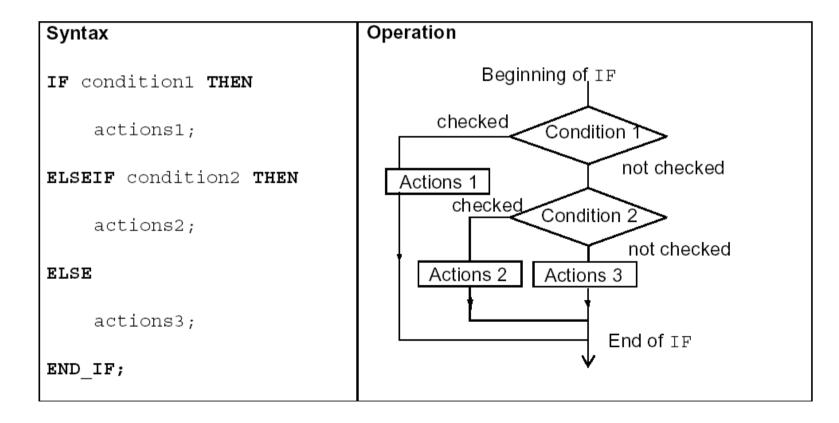

#### IF ... THEN ... ELSE ...

#### **Structures for Control of Flux**

#### WHILE

# Example:

```

! (*WHILE conditional repeated action*)

WHILE %MW4<12 DO

INC %MW4;

SET %M25[%MW4];

END_WHILE;

```

#### **Structures for Control of Flux**

REPEAT ... UNTIL

FOR ... DO

#### EXIT to abort the execution of a st6ructured flux control instruction

#### Example:

#### **Structures for Control of Flux**

#### Halt

Stops all processes!

#### Structured text language

```

IF %M10 THEN

HALT;

END_IF;

```

# **Events masking**

#### Structured text language

```

IF %MO THEN

MASKEVT();

END_IF;

IF %M8 THEN

UNMASKEVT();

END_IF;

P. Oliveira

```

# Data and time related instructions

| Name           | Function                                        |

|----------------|-------------------------------------------------|

| SCHEDULE       | Time function                                   |

| RRTC           | Reading system date                             |

| WRTC           | Updating system date                            |

| PTC            | Reading date and stop code                      |

| ADD_TOD        | Adding a duration to a time of day              |

| ADD_DT         | Adding a duration to a date and time            |

| DELTA_TOD      | Measuring the gap between times of day          |

| DELTA_D        | Measuring the gap between dates (without time). |

| DELTA_DT       | Measuring the gap between dates (with time).    |

| SUB_TOD        | Totaling the time to date                       |

| SUB_DT         | Totaling the time to date and time              |

| DAY_OF_WEEK    | Reading the current day of the week             |

| TRANS_TIME     | Converting duration into date                   |

| DATE_TO_STRING | Converting a date to a character string         |

| TOD_TO_STRING  | Converting a time to a character string         |

| DT_TO_STRING   | Converting a whole date to a character string   |

| TIME_TO_STRING | Converting a duration to a character string     |

# There are other advanced instrauctions (see manual)

- Monostable

- Registers of 256 words (LIFO ou FIFO)

- DRUMs

- Comparators

- Shift-registers

•••

- Functions to manipulate *floats*

- Functions to convert bases and types

#### **Numerical Tables**

| Туре           | Format         | Maximum<br>address | Size            | Write access |

|----------------|----------------|--------------------|-----------------|--------------|

| Internal words | Simple length  | %MWi:L             | i+L<=Nmax (1)   | Yes          |

|                | Double length  | %MWDi:L            | i+L<=Nmax-1 (1) | Yes          |

|                | Floating point | %MFi:L             | i+L<=Nmax-1 (1) | Yes          |

| Constant words | Single length  | %KWi:L             | i+L<=Nmax (1)   | No           |

|                | Double length  | %KWDi:L            | i+L<=Nmax-1 (1) | No           |

|                | Floating point | %KFi:L             | i+L<=Nmax-1 (1) | No           |

| System word    | Single length  | %SW50:4 (2)        | -               | Yes          |

#### Instruction list language

LD %M0 [%MW0:10:=%MW20:10+100]

LD %I3.2

[%MD50:5:=%KD0:5+%MD0:5]

# **Industrial Automation**

(Automação de Processos Industriais)

# GRAFCET (Sequential Function Chart)

http://www.isr.ist.utl.pt/~pjcro/courses/api1011/api1011.html

Prof. Paulo Jorge Oliveira pjcro @ isr.ist.utl.pt Tel: 21 8418053 ou 2053 (internal)

# Syllabus:

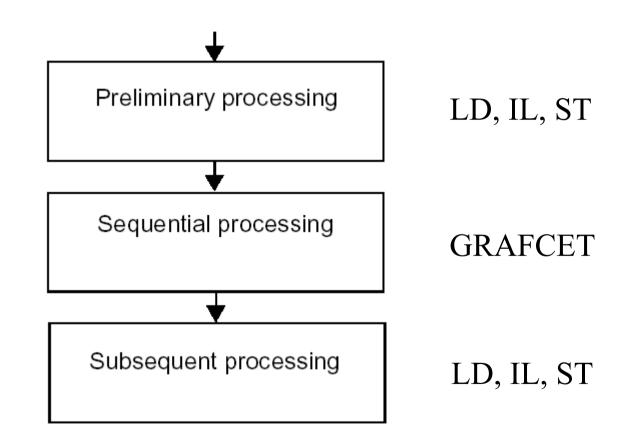

Chap. 3 – PLCs Programming Languages [2 weeks]

•••

Chap. 4 - GRAFCET (Sequential Function Chart) [1 week]

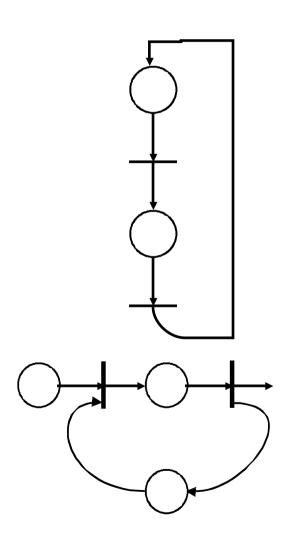

The GRAFCET norm.

Elements of the language.

Modelling techniques using GRAFCET.

• •

Chap. 5 – CAD/CAM and CNC Machines [1 week]

# PLCs Programming Languages (IEC 1131-3)

# Ladder Diagram

# Structured Text

If %I1.0 THEN %Q2.1 := TRUE ELSE %Q2.2 := FALSE END\_IF

# Instruction List

LD %M12 AND %I1.0 ANDN %I1.1 OR %M10 ST %Q2.0

# Sequential Function Chart (GRAFCET)

# Some pointers to GRAFCETs (SFCs)

History: http://www.ecsi.org/ecsi/Doc/OtherDoc/SLDL/PDF/caspi.pdf

http://www.lurpa.ens-cachan.fr/grafcet/groupe/gen\_g7\_uk/geng7.htm

Tutorial: <a href="http://asi.insa-rouen.fr/~amadisa/grafcet-homepage/tutorial/index.html">http://asi.insa-rouen.fr/~amadisa/grafcet-homepage/tutorial/index.html</a>

http://www-ipst.u-strasbg.fr/pat/autom/grafce t.htm

Simulator: <a href="http://asi.insa-rouen.fr/~amadisa/grafcet-homepage/grafcet.html">http://asi.insa-rouen.fr/~amadisa/grafcet-homepage/grafcet.html</a>

http://www.automationstudio.com (See projects)

Bibliography: \* Petri Nets and GRAFCET: Tools for Modelling Discrete Event Systems

R. DAVID, H. ALLA, New York: PRENTICE HALL Editions, 1992

\* Programação de Autómatos, Método GRAFCET, José Novais,

Fundação Calouste Gulbenkian

\* Norme Française NF C 03-190 + R1 : Diagramme fonctionnel

"GRAFCET" pour la description des systèmes logiques de commande

Homepage: <a href="http://www.lurpa.ens-cachan.fr/grafcet/">http://www.lurpa.ens-cachan.fr/grafcet/</a>

# History

#### **GRAFCET**

- 1975 Decision of the workgroup "Logical Systems" da AFCET (Association Française de Cybernétique Economique et Technique) on the creation of a committee to study a standard for the representation of logical systems and automation.

- 1977 GRAFCET definition (Graphe Fonctionnel de Commande Etape-Transition).

- 1979 Dissemination in schools and adopted as research area for the implementation of solutions of automation in the industry.

- 1988 GRAFCET becomes an international standard denominated as "Sequential Function Chart", pela I.E.C.

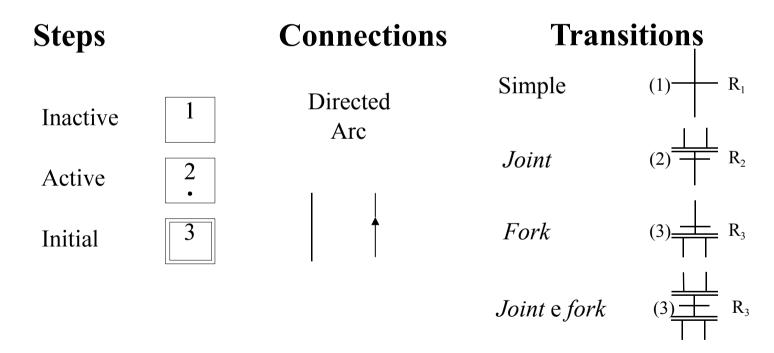

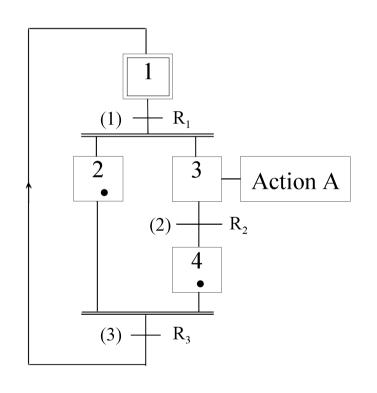

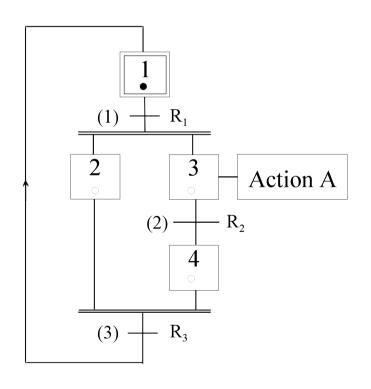

#### **Basic Elements**

Actions can be associated with Steps.

A logical receptivity function can be associated with each **Transition**.

Action A

$-R_2$

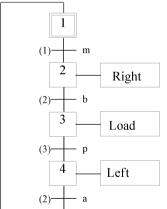

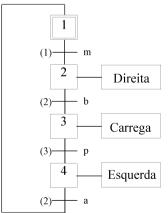

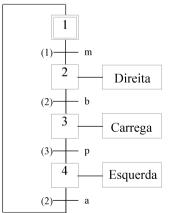

# **GRAFCET**

#### **Basic Elements**

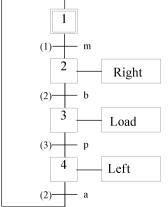

# **Oriented connections (arcs)**

In a GRAFCET:

An Arc can connect Steps to Transitions

An Arc can connect Transitions to Steps

A Step can have no Transitions as inputs (source);

A Step can have no Transitions as outputs (drain);

$\begin{array}{c|c}

\hline

2 \\

\hline

(2) \\

\hline

(3) \\

\hline

R_3

\end{array}$

(1) -

The same can occur for the Transitions.

$R_1$

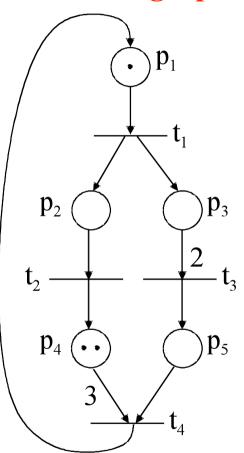

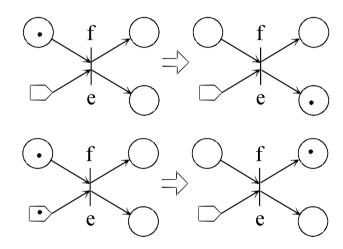

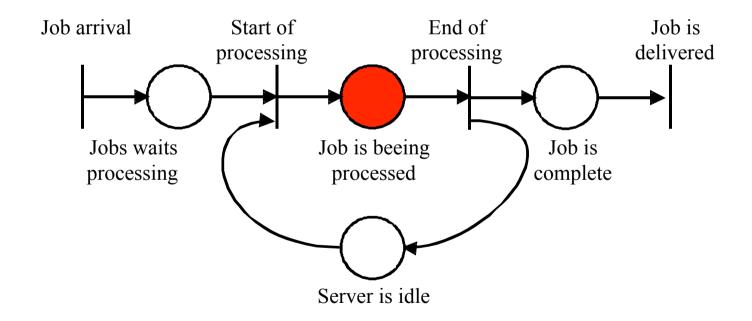

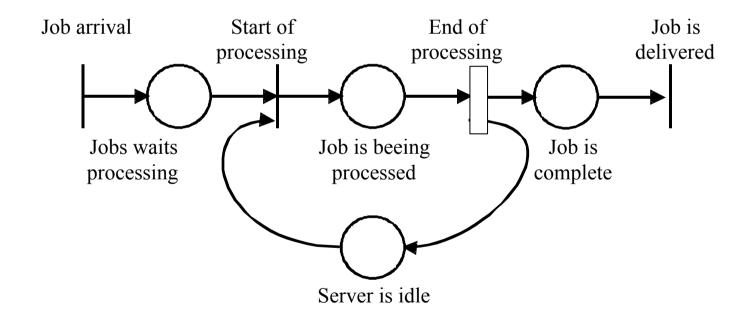

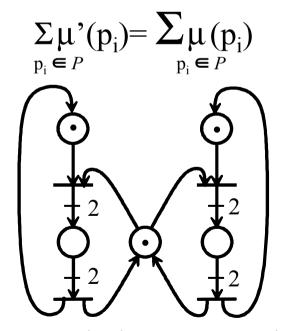

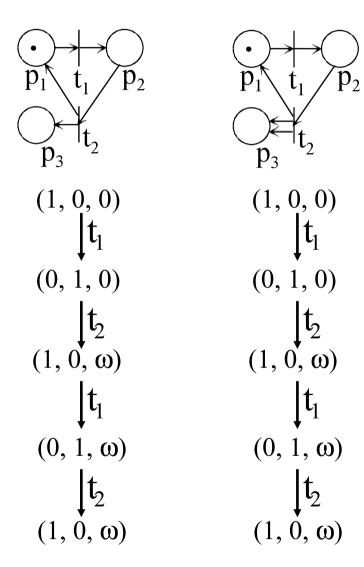

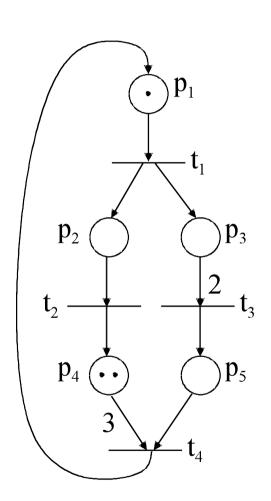

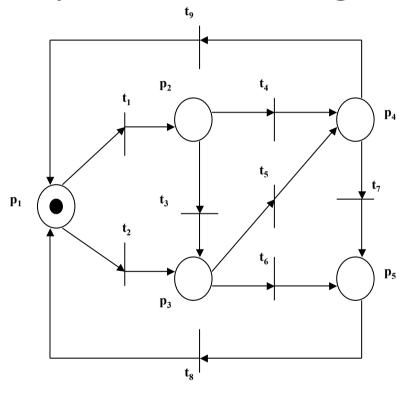

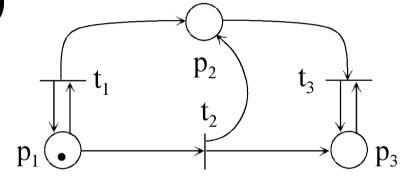

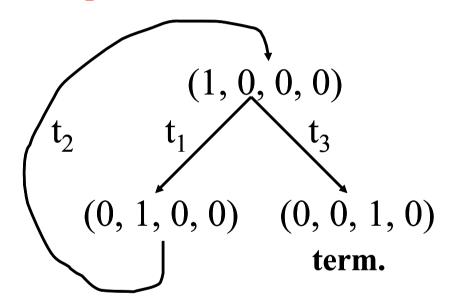

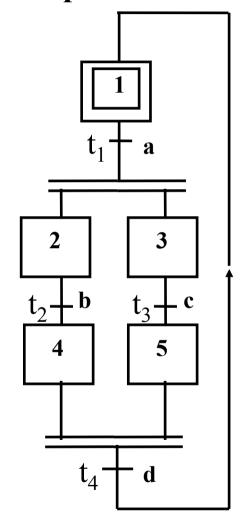

#### State of a GRAFCET

The set of markings of a GRAFCET constitutes its state.

# **Question:**

How evolves the state of a GRAFCET?

#### **State Evolution:**

• Rule 1: Initial State

It is characterized by the active Steps at the beginning of operation (at least one).

• Rule 2: Transposition of a Transition

A Transition is active or enabled only if all the Steps at its input are active (if not it is inactive).

A Transition can only be transposed if it is active and its associated condition is true (receptivity function).

• Rule 3: Evolution of active Steps

The transposition of a Transition leads to the deactivation of all the Steps on its inputs and the activation of all Steps on its outputs.

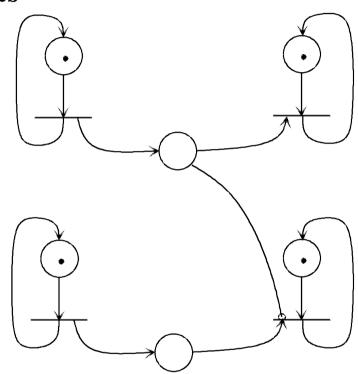

• Rule 4: Simultaneous transposition of Transitions

All active Transitions are transposed simultaneously.

• Rule 5: Simultaneous activation and deactivation of a Step

In this case the activation has priority.

# **State Evolution:**

#### • Rule 2a:

All active Transitions are transposed immediately.

#### • Rule 4:

Simultaneous active Transitions are transposed simultaneously.

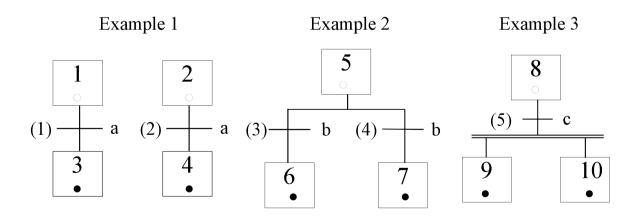

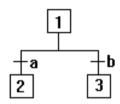

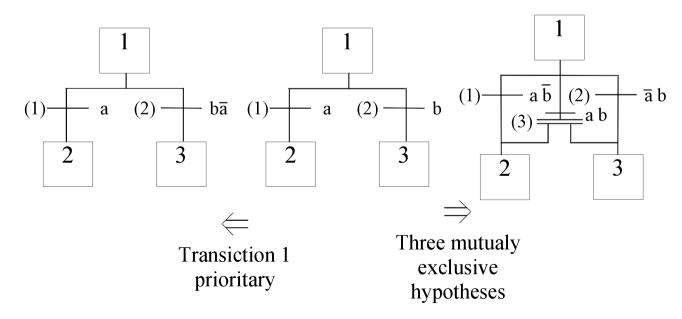

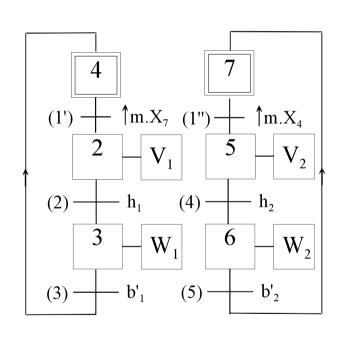

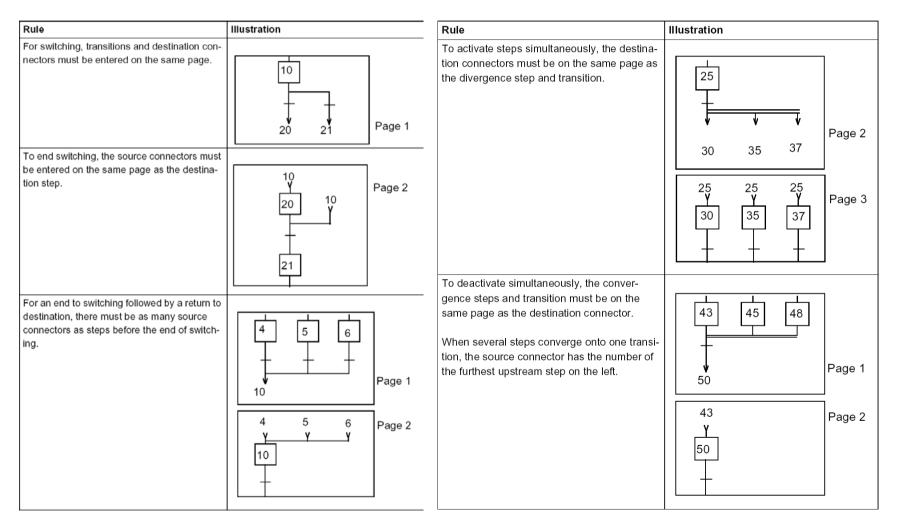

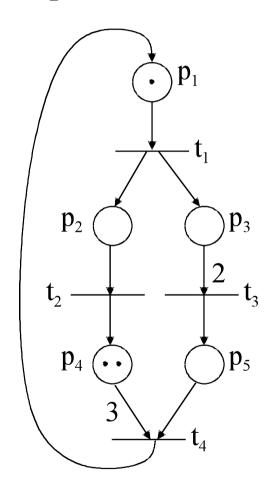

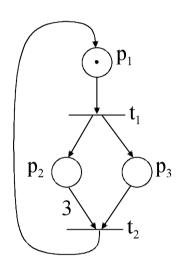

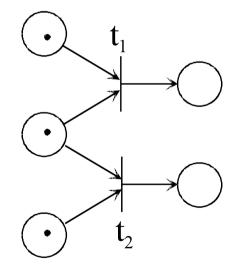

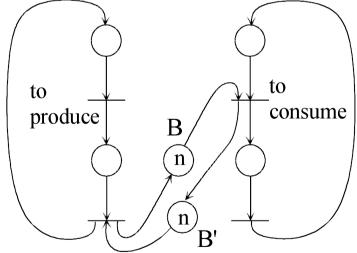

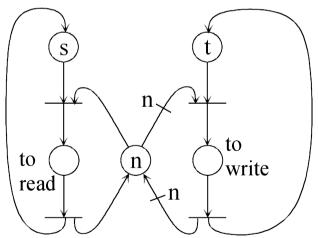

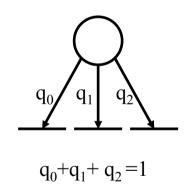

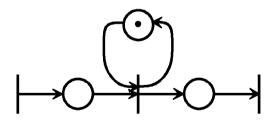

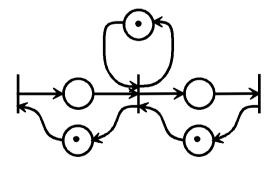

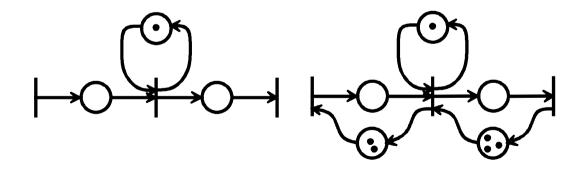

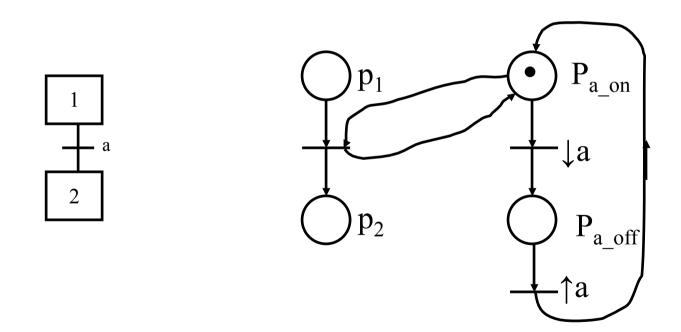

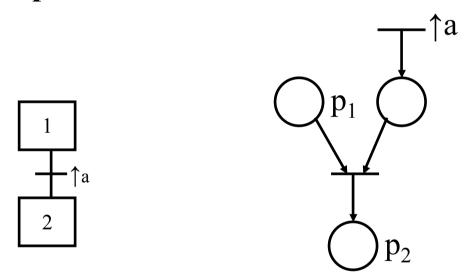

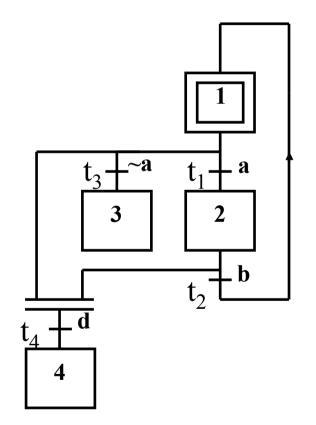

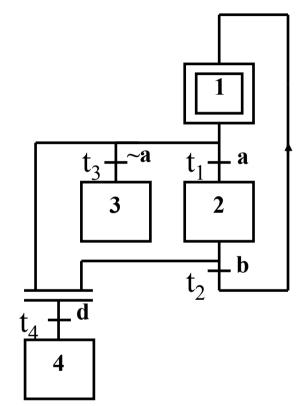

# OR Divergences:

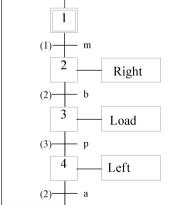

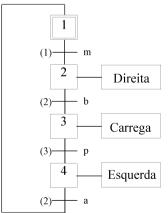

If Step 1 is active and if **a** is TRUE then Step 1 is deactivated and Step 2 is activated (state of Step 3 is maintained).

If **a** and **b** are TRUE and Step 1 is active then Step 1 is deactivated and Steps 2 and 3 are activated (for any previous state of Steps 2 and 3).

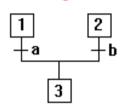

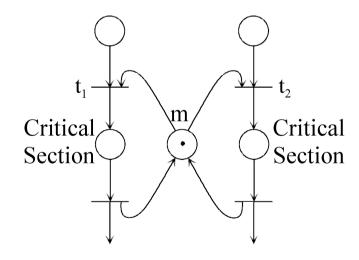

## OR Convergences:

If Step 1 is active and if **a** is TRUE then Step 1 is deactivated and Step 3 is activated (state of Step 2 remains unchanged). The same happens for Step 2 and **b**.

If both Steps 1 and 2 are active and **a** and **b** are TRUE then Steps 1 and 2 are deactivated and Step 3 is activated.

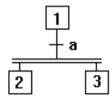

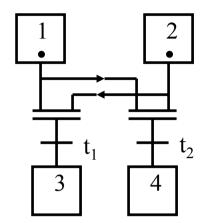

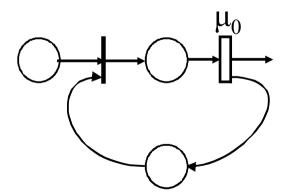

#### AND Divergences:

If Step 1 is active and if **a** is TRUE then Step 1 is deactivated and Steps 2 and 3 are activated.

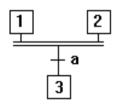

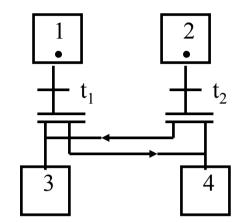

# AND Convergences:

If Steps 1 and 2 are active and if **a** is TRUE then Steps 1 and 2 are deactivated and Step 3 is activated (if only one of the input steps is active, the state remains).

Example:

**GRAFCET** state evolution

Level activated Action. Actions can also be activated during transitions - see next.

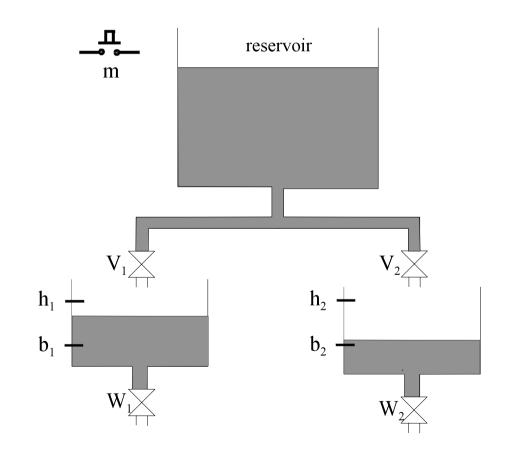

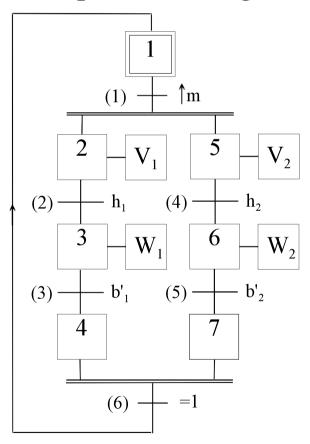

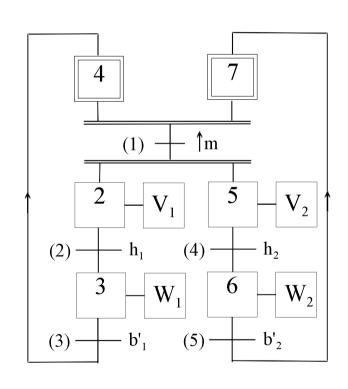

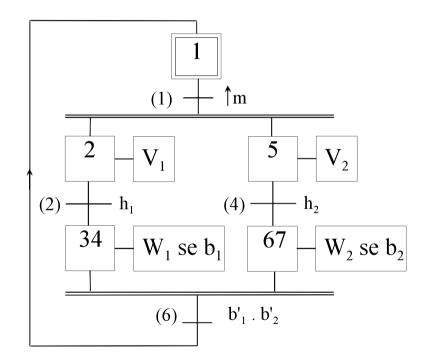

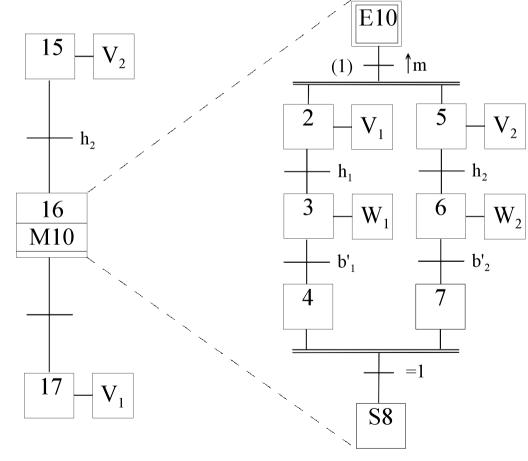

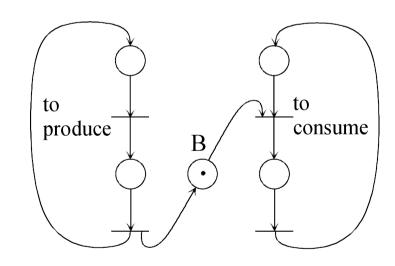

## **Modelling problem:**